关于不同工艺节点mos VTH的短沟道和反短沟道效应解释

最近看到有帖子讨论mos VTH的问题,我记得好几年前就在坛子里回帖子解释过这种现象,不过回帖找不到了

可能是大家对工艺和器件不太熟悉,对于不同工艺节点,表现出来VTH vs Length的现象时不同的

大家正常思维都是短沟道效应,length越短,Vth越小,这只是DIBL效应,针对比较老的工艺和器件结构是适用

但是从180nm开始,器件结构改变,大家也许听说过halo结构吧。自从有了halo结构,大家经典的SCE 效应思维就不适用了

由于工艺越先进,length越小,源漏穿通punch through越容易发生,大家都知道PN结耗尽层宽度与掺杂浓度有关,由于S/D必然是重掺杂,沟道浓度较低,沟道耗尽层也较宽,当S/D两边耗尽层相连,也就开始发生punch through现象,出现mos管无法关断。

halo结构就开始被普遍采用,阻挡源漏PN结的扩展,克服短沟道器件的punch through现象。

halo结构就是在MOS沟道中靠近源漏S/D PN junction的地方做两个与沟道同型的重掺杂,可以有效阻止耗尽层向沟道中扩散,从而阻断punch through 的发生。

接下来我们分析为什么halo结构会产生RSCE也就是反短沟道效应,length越小 Vth越大

大家都知道半导体工艺的按比例缩小规则,其中有一条就是要提高沟道掺杂浓度,保持Vth不变,说明沟道浓度与Vth直接相关,当然Vth的公式也写得很明白,我就不用写出来了,我们是做电路的,对于器件和工艺只要定性的了解和知道原理和趋势即可。

由于halo结构是做与沟道同型的重掺杂,等效于提升沟道平均浓度,那么Vth自然会随之提升,当mosfet Length增加,沟道平均浓度下降,Vth也随之下降,这就是我们看到的现象。

当然这时候穿通的SCE、DIBL效应也是存在的,我们看到的是两者综合的效应,有时候会出现Vth随L先增大后减小

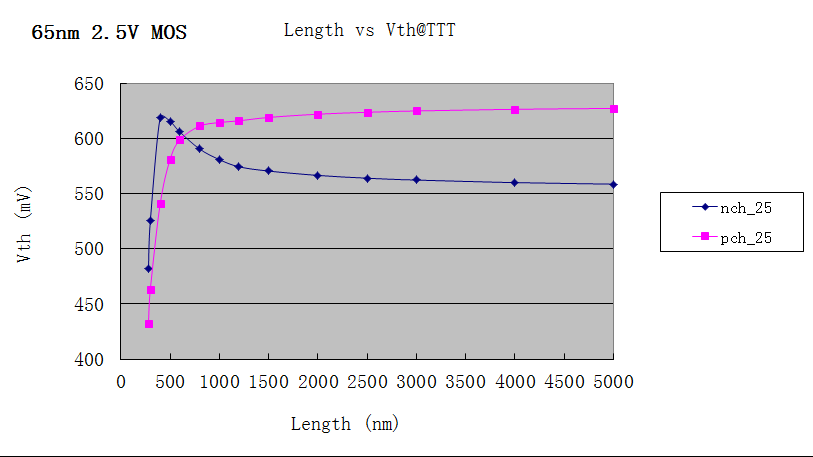

画了个示意图,不过画的有点难看,凑合看吧,还有以下这个65nm工艺1.0V device 和2.5V device的 Vth随Length的变化趋势。对于不同工艺,通常会有所差别。

很不错,应该多点这样的贴

受益匪浅,能不能再深入讲一下pch25和其他管子不一样的原因?

另外请教,core器件halo是做在ldd下面,那么IO器件可能没有ldd,那么halo怎么做呢?正常的case,2.5V device 是不做halo结构的

纯粹的科普贴,纯粹的贡献贴,非常感谢小编。

Thanks very much~

嘉

好贴。

学习了,谢谢小编

感谢小编分享

学习,学习。

必须顶上去!

学习了!支持无私奉献的精神!

顶一下,有人说我言而无信

nicer

大神啊,科普了,我就说为什么最近用65nm工艺做的时候,仿起来和书上说的不一样

最近正受这个问题困扰,非常感谢小编!

学习~

为什么2.5V pMOS的Vt还上升尼,没有halo的话

感谢小编分享

好帖子,讲得很详细

mark。

赞你的贡献分享精神!

谢谢总结!受教了!

请教小编:有的工艺没有halo结构也有RSCE,如何解释?

请教:2.5V的 没有halo结构,为啥也有RSCE呢?

正在做65nm的芯片,刚好遇到这种问题。这下解决了

GOOGLE FIND

对于0.5um或者0.35um以下工艺来说,使用的RTA工艺,主要由小编所说的注入引起;

对于0.5um以上,使用炉管工艺,主要由瞬态增强扩散引起。

yahoo 知識

隨著閘極通道長度(gate length)越變越短,短通道效應(short channel effect)就愈益明顯,短通道效應有許多現象,其中之一就是臨界電壓(Vth)變小,造成漏電增加,但是我們有時會發現 Vth 卻反其道而行,通道長度越短,Vth 卻有增加現象(以 NMOS 為例),當然如果再更短的話,可能 Vth 又有變小的趨勢,總而言之,在 NMOS 中,Vth 隨著通道長度變短而變大的現象就叫 reverse short channel effect,PMOS 的話則是 Vth 變小。

最常見的一個例子是,為了要減輕短通道效應,以 NMOS 為例,我們會在 N+區域的角落打上 P-type 的 implant,叫做 pocket implant,當通道長度越短,源極汲極打的 pocket implant會越靠越近,無形中這種 p-type的 implant會重疊,好像另外一個 p-type通道一樣,通道的 p-type濃度升高了,自然 Vth 也提高了

MORE見 965301009矽鍺 P 型通道電晶體於外加單軸應力下之溫度效應分析

論文

pages15在元件尺寸微縮效益下的同時,金氧半場效電晶體將面臨到短通道效應

(Short channel effect),導致電晶體工作特性之退化。因此,本節中將對於

SiGe-Channel pMOSFETs 於尺寸微縮下進行分析。通道長度愈短,短通道效應就

愈明顯。短通道效應將造成臨界電壓下降 (V th roll-off)。再者,源極與汲極端的

空乏區容易重疊在一起,使得元件漏電流增加。為了減輕短通道效應所導致的臨

界電壓下降,目前最常使用抑制的方式為口袋式佈植(Pocket Implant)去提高基板

的摻雜濃度。以 PMOS 為例,會在源極/汲極區域側邊植入 N 型元素(如:砷或銦)

以形成一高摻雜濃度佈植區,以防止源極與汲極端的空乏區重疊。然而,因為提

昇了基板中濃度,其元件的臨界電壓也因此提升,此為反短通道效應( Reverse

Short Channel Effect ;RSCE),如圖 2.7 所示。通道長度越是縮減,反短通道效應越明顯

3ku,...