关于带隙基准的问题(有经验的兄弟指点一下)!

用SMIC.18工艺

一直有许多疑问

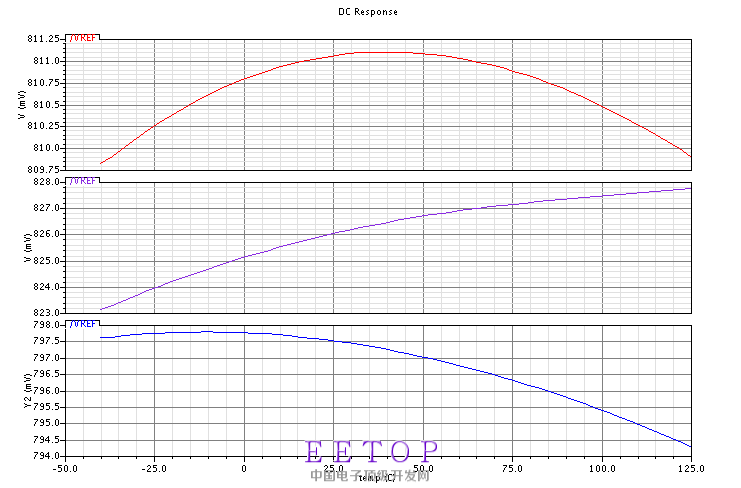

温度系数仿真下来可以大概10 PPM/C

(各个工艺角都跑了)

但是发现每个工艺角下的Vref都是偏差很大啊!

例如:在20C下,在FF角下,Vref=1.17 V.在TT角下,Vref=1.155 V

在SS角下,Vref=1.145 V

就是说明将来流出来的片子,片子间的输出Vref将有很大的偏差!

这对于A/D来说会不会是致命的?

听师姐说,每个A/D在电路工程师应用时,要调满量程的,所以关系不大

但是我老是觉得这工作量太大了吧!效率忒低了

同疑惑

同疑惑:

不同的工艺角下差数差别那么多,流片后的冬冬会不会有问题啊?能用吗?

很少adc 会运行在 full scale, 大部分都是-1dB.

-1dB 就是90% full scale. 10mV 的变化无所谓的。

ADC 不会对这么点区别敏感

一般做运放都需要Trimming吧

仿真和实际流片出来是肯定有差别的。特别是到了量产阶段。每个批次的差别也是很大的。这样的我们只能加入trim 。只要修调到能隙值,就能保证温度系数基本上很小。

回复

我之前也仿过,差别也很大

非常正常的一个现象。不用担心。

等你tapout后,你会发现vref也会有几个milli的向上或者向下的漂移。

由于不同的工艺模型所产生的偏差,这是正常现象。

To derease the BGR deviation, 3*sigma (or 6*sigma) design is a must. Then, after wafer-out, you could find 99.6% die drop in your target range.

不是fullscale,SNDR这些不变就没事。

不同工艺角的VREF要怎么仿真啊

带隙基准基准肯定是要trim的

对模拟电路,corner并不非常有用

要用统计模拟和montacalo分析!

要作个bandgap trim 电路

没有经验,努力学习当中!

1. If you care about absolute value, trimming is a must. No one can do 1% accuracy without trimming in the world.

2. Many many ADC do NOT require absolute accuarcy. That is to say if you get +/-3% without trimming, it will be acceptable.

However, for temp. coef., some applications require as flat as possible for Vref vs temp.In that case, you need compensate temp. effect only. Let alone the variations for Vref vs P(as long as +/-3%)

这个应该会有影响吧

你好,我也用smic 0.18um调带隙,但是温度系数相差很多,请问怎样调到一样。不胜感激!

跑一下MISMATCH试一下,就是蒙特卡洛