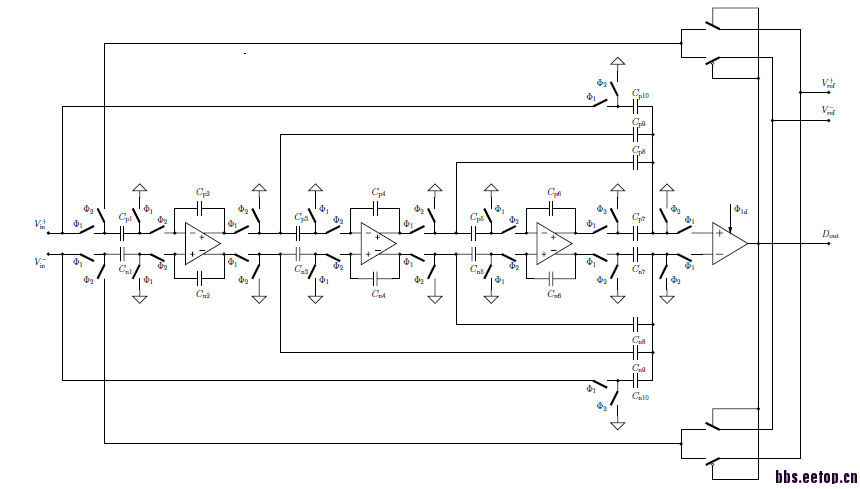

单环3阶CIFF结构sigma-delta设计问题

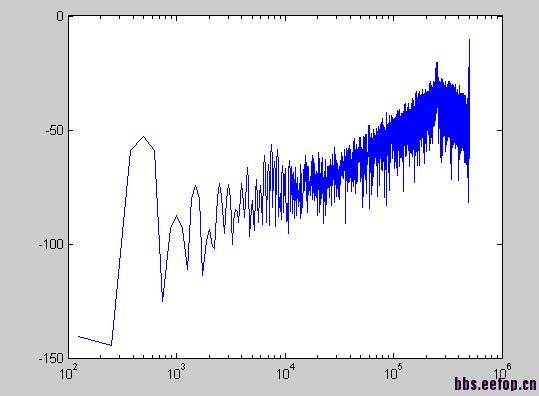

最近在学习sigma-delta modulator,在用matlab实现系统级仿真后,现用spectre搭建理想电路进行行为级仿真,开关为理想开关,运放与比较器均用VCVS搭建,比较器的输出直接反馈到VREF的控制开关。输入正弦小信号,将比较器输出码在MATLAB中进行FFT分析后发现性能相当差,请教各位是哪些电路的哪些方面可能出了问题

自己顶一下,是不是因为比较器在phase1进行比较并输出电平,而VREF反馈在phase2工作,这样就不能直接将比较器输出反馈到VREF的控制时钟上,而需要做个时序逻辑呢

有个疑问,为什么要输入这么小的信号,能不能给个至少-6dB信号的图 ?

有个疑问,为什么要输入这么小的信号,能不能给个至少-6dB信号的图 ?

谢谢小编,正在用-6db信号在跑,您提醒前确实忽略这个问题,一直以为自己做的时序出问题了,但总找不到问题在哪

小编,又要请教问题了,1、我在加入-3db信号以后信噪比大概是90db左右(纯粹理想电路,换了几组系数都这样),但用simulink进行系统仿真时,SNR能达到125db以上,是什么原因导致信噪比下降这么多呢

2、如图结构中的构成加法器的电容该取多大的值合适呢(这几个电容和前面的电容不存在比例关系啊,如何将系数转换成电容值),我取值在几百fF,合适吗?

加法器电容应该比积分器中的电容小一些,个人看法,

希望大牛出来指点。

看了好多文献都没有提到相关的东西,目前我设置的为几百个fF,但是结果还是不够好,还在查找原因中

请问有结果了吗,我也是很纳闷怎么将系数转换成具体电容值

j是不是没有进行相干采样

感觉PSD中有很大的谐波啊。

按照比例换。然后考虑电容大小带来的噪声与速度影响。

小编,我做出来老CIFF结构的SDM,512的过采样率,信噪比才50DB,请问都有哪些原因啊?

你好,小编,你设计的比较器输出,用matlab进行FFT分析,能提供一下matlab相关的程序吗?还有你的spectre仿真的数据时导出什么格式的数据,导出流程能否说一下啊,谢谢小编。

信号中是不要加入直流电压,加法电容值当然是小的好,省面积,但是他们之间要满足一定的比例关系,还要看一下你的matlab数据处理时的信号泄露。

估计是积分器和PSD模块参数设置问题

顶一下,谢谢分享!

严格的说是-6dBFS

他加hann窗后 做fft时也要refer到0dBFS,那个频谱看起来才方便

小编,您好。我最近也在学习三阶CIFF结构sigma-delta。请问设计系数就是利用的delsig里的dsexample1算的吗?算得系数后利用simulink的模型仿真,SNR就非常小。不知道是什么原因?