PLL的锁定过程

三个问题:

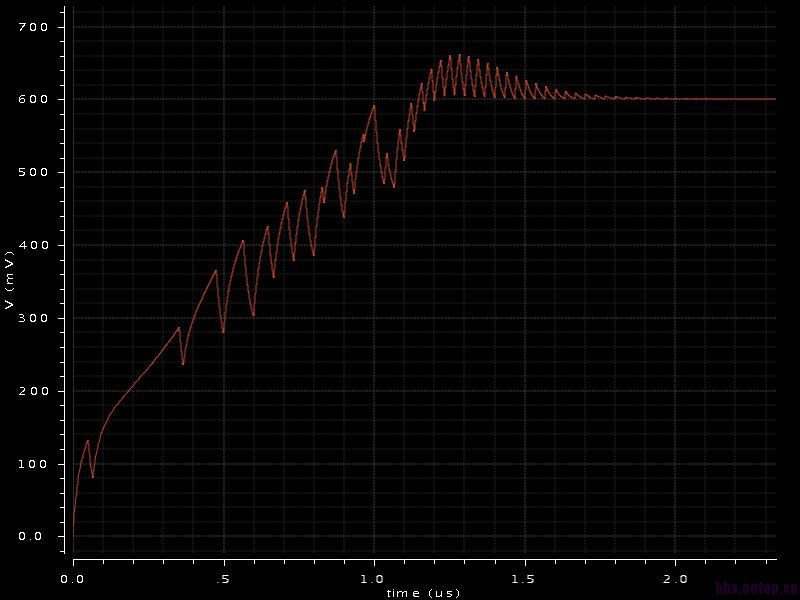

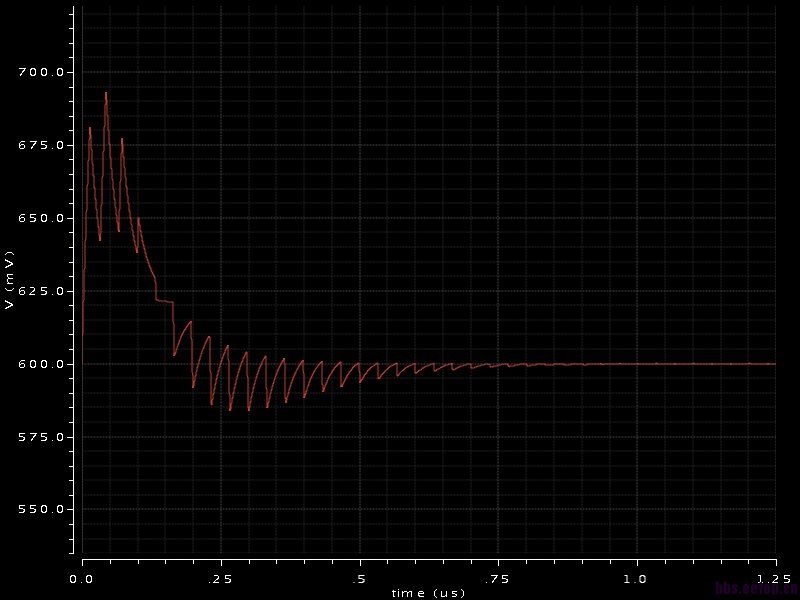

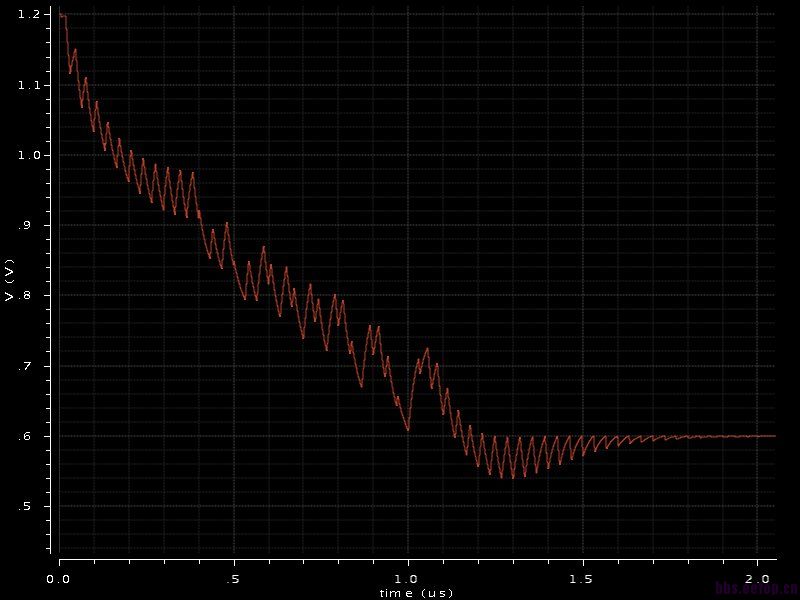

(1)上面三图分别是电容初始电压为0V,0.6V,1.2V时的PLL锁定过程,我一直还是无法理解在锁定过程中出现的类似锯齿波的形式,电压一会儿上升一会儿下降,请问出现这种现象的原因是什么?

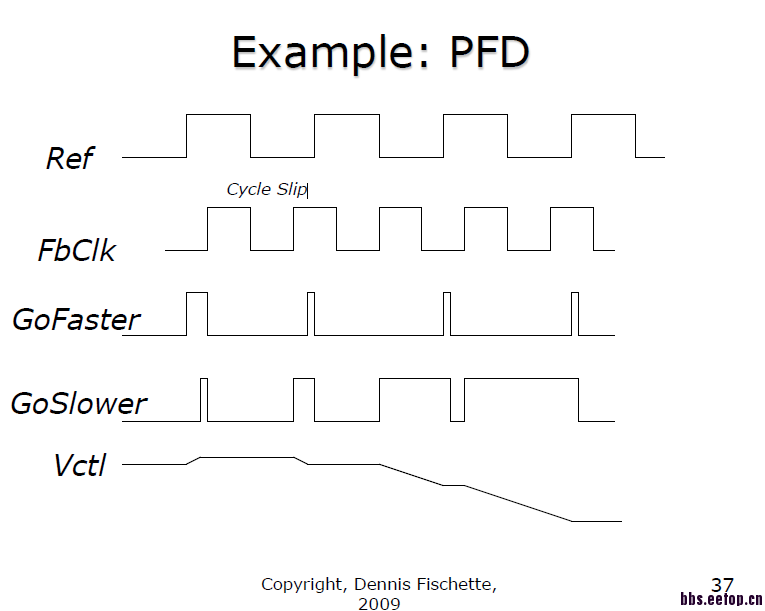

(2)我现在在研究不改变环路带宽和参考频率的情况下如何去使这个锁定时间进一步减小,当然快速锁定方法是一种,我在想可不可以对这个图中的锯齿波下功夫,使之不会出现上下波动,从而优化锁定时间,听说可以改变PFD的结构,不知哪位大神思考过这个问题或者遇见过与之相关的文献资料,望共享,不胜感激!

(3)看过一个PPT上面讲过说是 cycle slip导致的 ,我对这个解释还是不够清楚,望大神补充!

你到底需要多长时间lockin?现在时间也不是很差。

锁定时间是不错,我只是想进一步去研究这个问题,再去优化而已

mark先看看

充电时电阻上有压降,并且是先充电到小电容上,然后再分到大电容上,电压就这个样子。

谢谢你的回复,你的意思是先充电到小电容上导致控制电压迅速上升,然后小电容上的电荷放电分到大电容上导致电压下降,从而形成类似的锯齿波?

对的,还有R上的IR电压

谢谢你的回复,你可以看一下我的第一张图吗?我有一个疑问,控制电压从初始态0V慢慢上升到终值0.6V,为什么这个曲线不是一直单调上升最后到达0.6V不变? 而是快接近0.6V时先上升有一个过冲然后再慢慢下降平稳至0.6V呢?谢谢指教

我看了一下第一张图的那个过冲,过冲最高处都接近0.66V了,如果我的VCO在0.66V的时候都起振不起来了也就是过载了,或者VCO在0.66V之前基本上频率已经上不去了,那会有什么样的影响呢? 这个时候整个环路还能锁定起来吗?如果环路依旧能够锁定起来,那这个时候锁定过程的曲线是不是就不会有过冲了,因为已经冲不上去了?这个时候锁定时间我感觉反而会小一点?我还是一个菜鸟,希望能与大神有思想上的探索,不胜感激

我是看了这个帖子之后觉得应该思考一下这个问题的http://bbs.eetop.cn/thread-359727-1-1.html

http://bbs.eetop.cn/thread-359727-1-1.html

二阶系统基本都有过冲,PLL过冲肯定有的。如果0.6V对应的频率比如是1G,在0.66V只要能比1G多一点就能锁定到1G,比如1.01G,但是如果在这个电压段KVCO变化很大(变的太小)有可能会影响稳定性。如果出现非单调,肯定是不行的。

你好,谢谢你的回复,你的说在这个电压段如果Kvco变得很小,有可能会影响稳定性,是不是这个时候环路增益太小或者说由于Kvco太小导致环路带宽太小从而极大的影响了相位裕度使相位裕度严重变小,从而变得不稳定呢?

是的,只是有可能。

谢谢,你一般设计VCO的输出频率范围和实际PLL输出范围相比,VCO要留有多大的裕量呢?

后仿真10%-20%

不太明白,充电怎么有先后顺序。

赞一个