如何调整CPPLL的输入信号使得锁相环锁定?

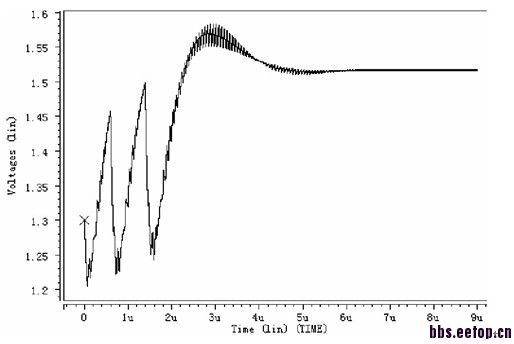

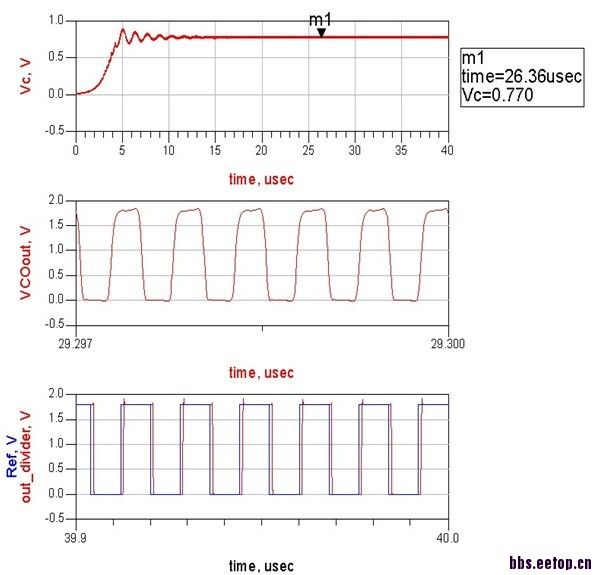

为什么我仿真的结果是下面这个样子的?没有锁定吧?怎么调节呢?参考信号Ref的周期应该调大还是调小呢?试了很多次都还是不行~

在仿环路锁定之前,你确定如下两点了?

1) 理解每个子模块的功能,单独仿真每个子模块功能都与预期一致;

2) 理解环路参数的意义,并且分配了合理的环路参数。

如果上面两点你没做到,仿一个环路锁定有什么意义?不锁定,你不知道问题可能出自哪里;即便锁定了,你也是瞎猫碰到死耗子。

如果上面两点你做到了,环路锁定还需要仿真?

说点粗浅之见:

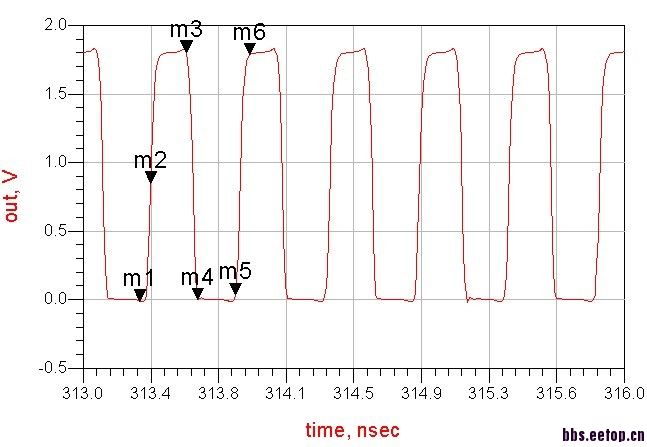

上图发生了一些cycle slipping现象,说明Fref比PLL带宽要高不少。

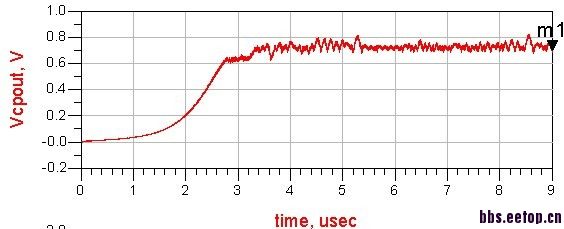

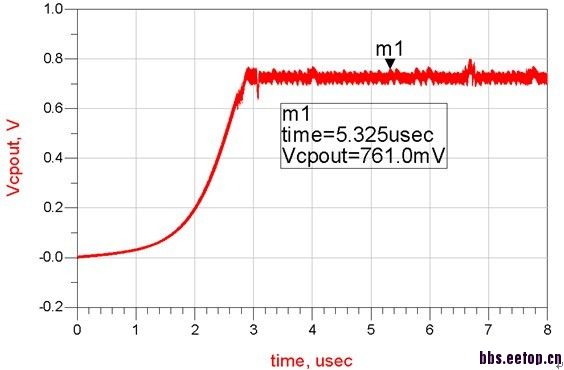

下面两图都是锁定快,jitter大的情况,说明此设计PLL带宽相对较大。

你还是要分析PLL环路特性,试Fref说不过去。

不好意思,我可能表达有误,我的意思是想说:是不是Fref不在锁定范围内,所以锁定不好。

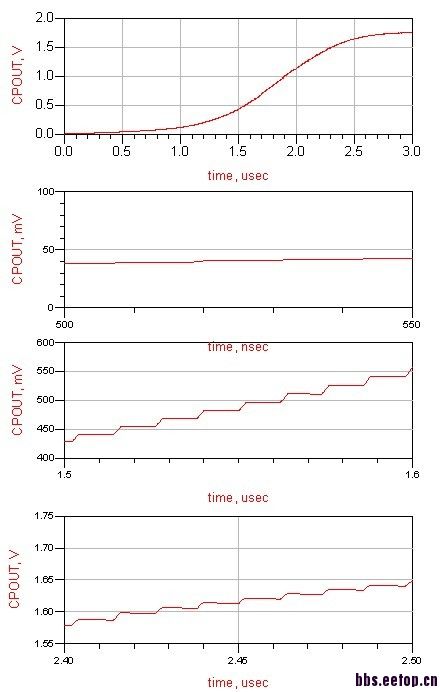

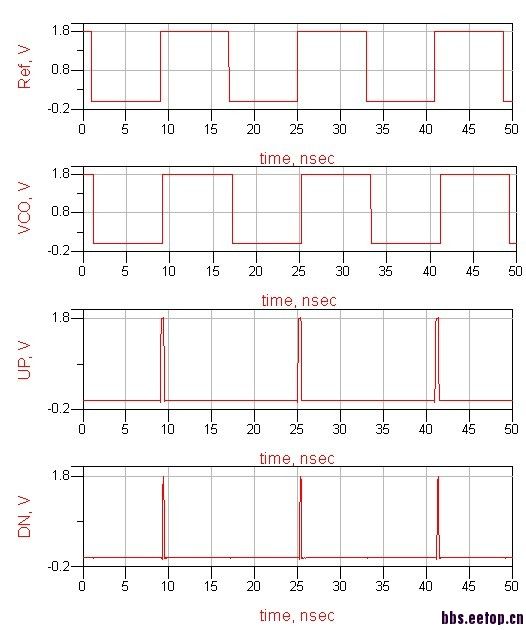

我单独仿真每个模块(PFD、CP、VCO、Divider都仿过了,LPF的值计算通过ADS中的

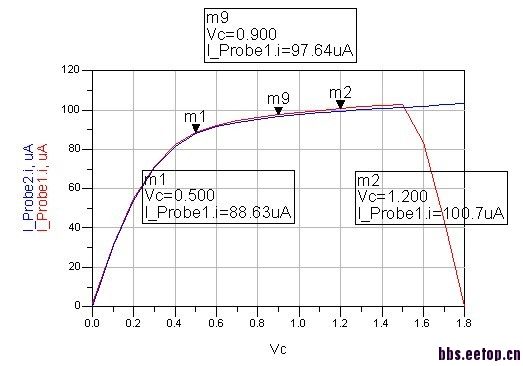

PLL_DesignGuide优化得到的)所得的结果都比较理想(如下几幅图),

PFD :

CP(充放电电流匹配曲线、充电及放电电压曲线):

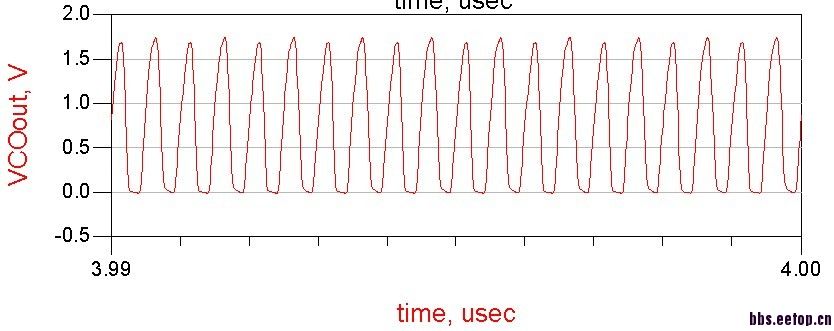

VCO经过整形后的输出端电压:

32分频结果:

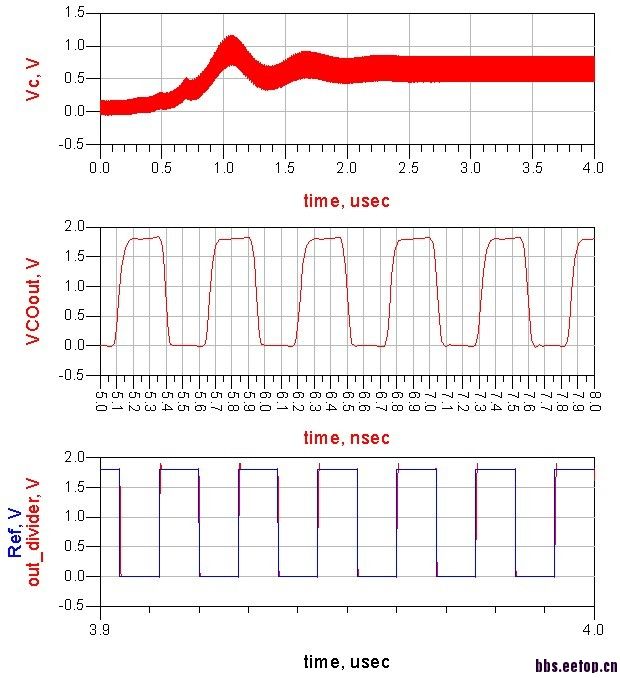

但是将5部分连起来后,发生频率牵引还有前后级的互相影响后,系统响应如下:

仅从Ref和分频器输出信号out_divider来看,CPPLL是锁定的(波形重叠了),但是从VCO输入端

的控制电压Vc来看貌似没有很好地锁定,不知道哪里出了问题呢?

而且VCO输出端的输出电压不如单独仿真时接近理想矩形波,如下图,是上升沿、下降沿延迟的问题吗?

具体如何解决呢?

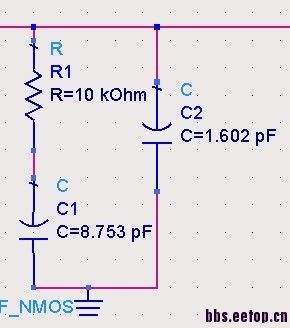

另外一个重要的问题:不是很清楚LPF该如何设计,我只是从一些论文里看到普遍采用

下面这种二阶无源滤波电路:

而其中的电容电阻有两种方法可以得到:一是按照一篇博士论文上介绍的方法计算得到(貌似普遍采用),

另一种是采用ADS中PLL的DesignGuide优化得到(我采用优化值)。

不知道哪种方法更准确呢?还有就是采用这种滤波电路还是采用三阶无源滤波电路低通性能更好呢?

这部分比较薄弱,望高手指教一二。

建议先把二阶的调好

学习一下你说的薄弱环节:环路计算

相位裕度合理些,Fref取pll带宽十倍或者以上

感觉是没有设计好补偿电阻电容的参数,带宽太大了。

恩,我再自己琢磨琢磨~

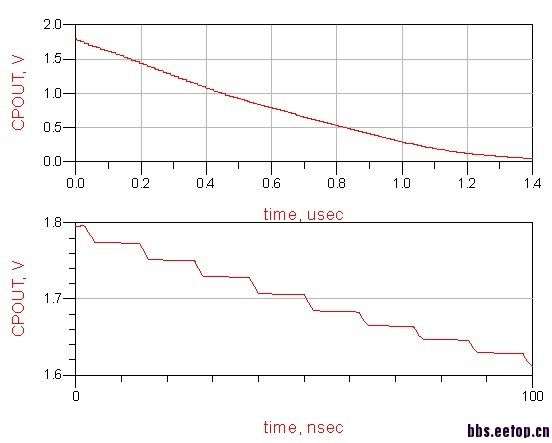

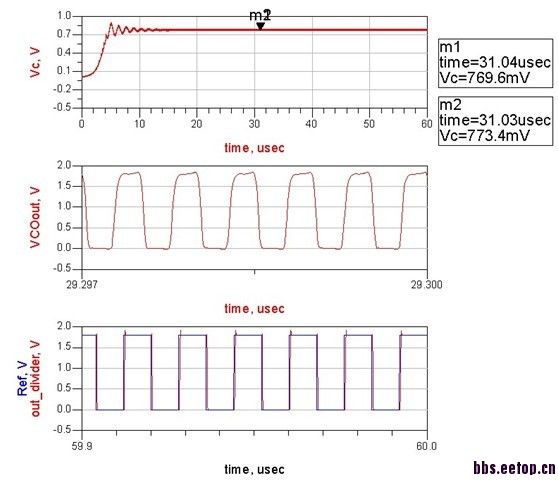

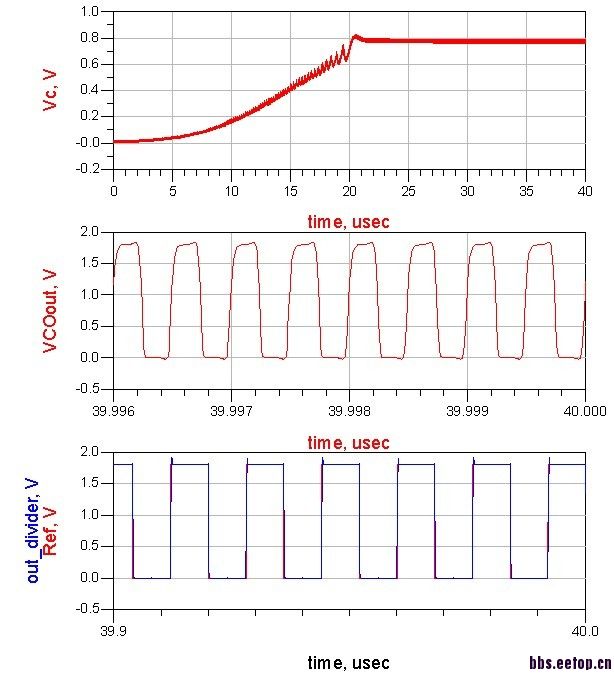

修改了一些参数后,得到的系统响应(VCO输入端压控信号)、VCO输出端电压曲线、PFD输入端参考信号及VCO输出信号分频后的信号(两信号重叠了)如下图:

这种情况能看成锁定吗?不知道为Vc那么粗?

求解答

小编,暂时别看transient。

你把各环路参数贴出来给大家看看。

Fref、Icp、R1、C1、R2、Kvco、feedback divider N

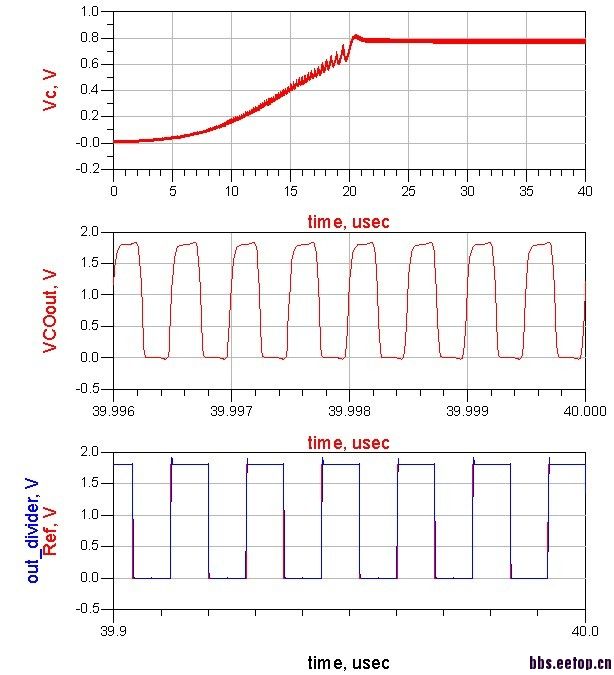

你好,我减小了环路带宽(增加电容大小)后仿真结果变好了(如下图),

但是PFD的两输入信号总相差一个固定的相位差,该如何减小这个相位差到零呢?

( 放大Vc可以发现15us之后Vc虽然稳定了,但还是存在微小的抖动)

Fref=62.5MHz;

Icp=97.64uA;

R1=20k;

C1=0.8nF;

C2=0.06nF;

Kvco=466.7MHz/V;

N=32

VCO中心频率:2.016GHz;

电源电压:1.8V

电荷泵充放电电流非匹配? 还是滤波器漏电?或是其它

我将仿真时间加长进行再仿真,发现PFD两输入信号的相位差减小了,几乎为0。

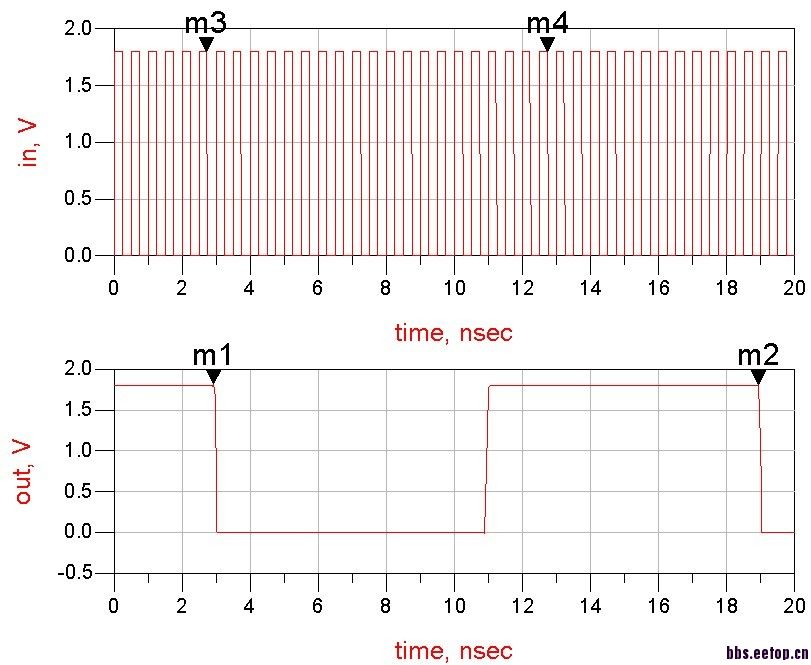

现在出现一个新问题:之前PLL系统仿真结果是:

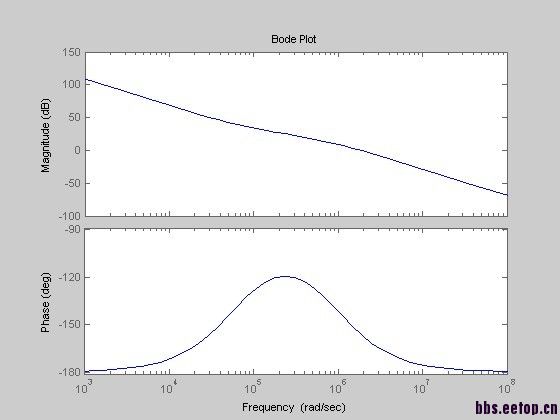

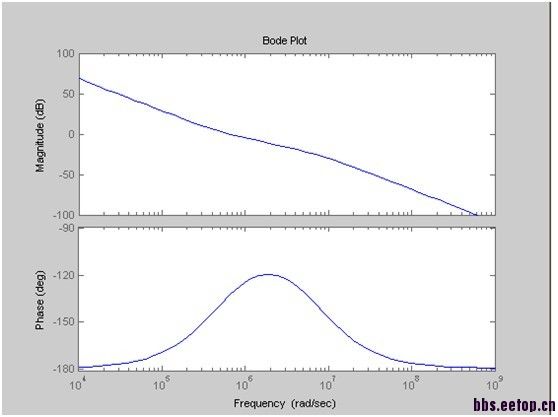

但是上面这个PLL对应的环路滤波器的相位裕度(如下图,不在45-60之间)

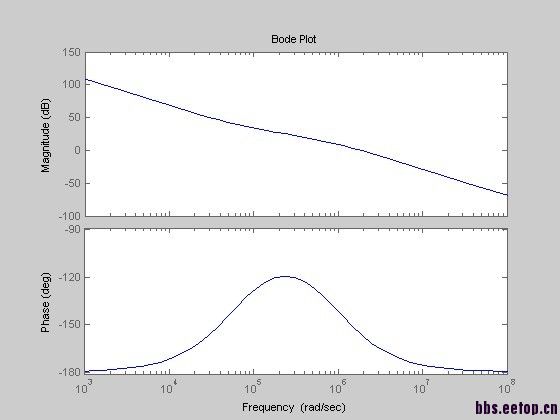

所以我修改了一下环路滤波器的参数,得到的PLL系统仿真结果和相位裕度结果如下两图:

相位裕度满足了,为约48.3度,但是系统仿真VCO控制端的控制电压过阻尼好像不太明显,需要吧阻尼调明显一点吗?

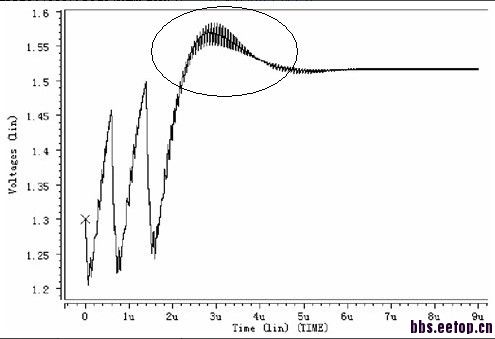

就像下面这个图一样,凸起大一点(画圈部分):

最后两个图重复的

哥们你这是ADS仿真吗?请问你的具体模块是用什么做的?晶体管搭的吗?

电容是不是有点太大了啊滤波器引入的极点1/R1C2比环路带宽还要大相位裕度不会太好的

我也与小编遇到了同样的问题, 请问小编这个问题是怎么解决的呀?

谢谢~