一种新颖的LDO结构

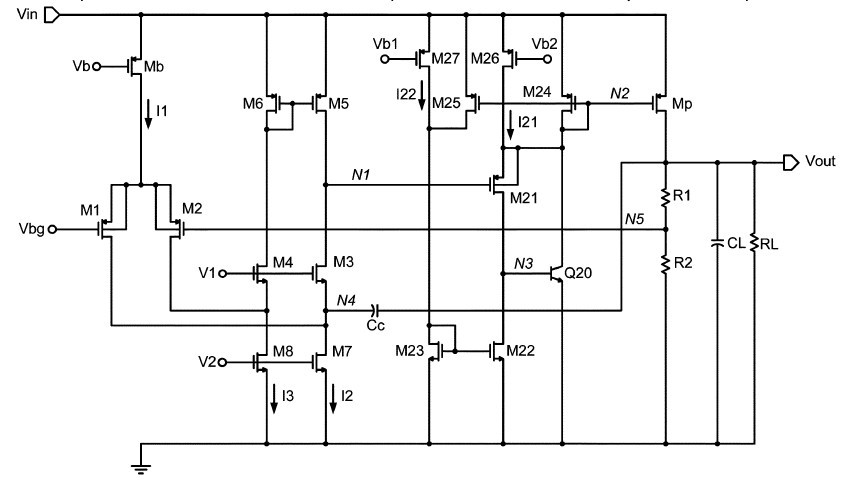

为了解决上述帖子中提到的问题,只能通过降低LDO带宽来实现,而传统结构降低带宽比较困难。目前找到了一种比较好的结构如下图:

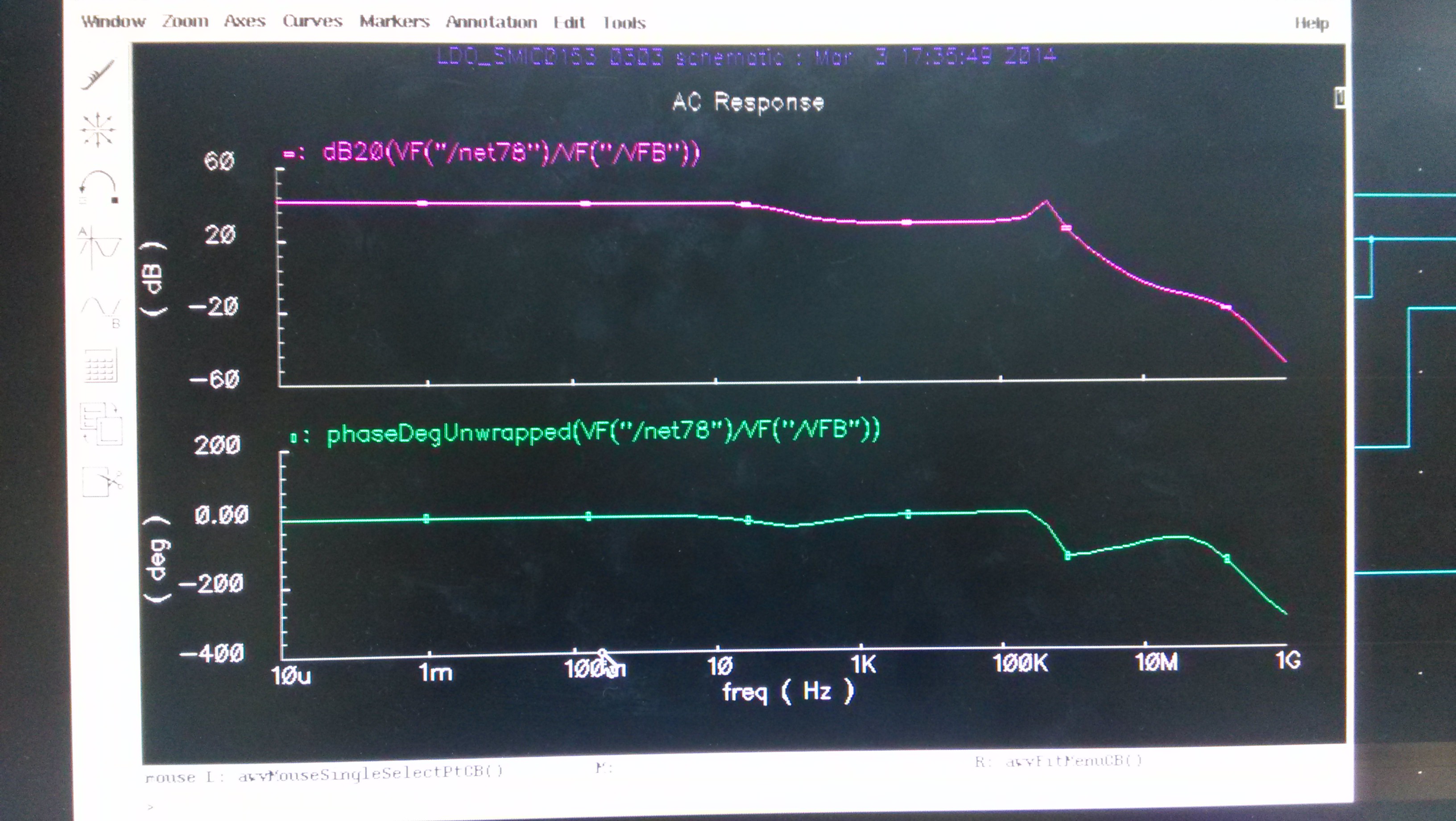

断开反馈环,进行AC仿真时发现从M2 Gate到N1节点的频响曲线如下图,纳闷的是:为何在500kHz处,增益出现尖峰,而相位急剧下降。

从bode图中看应该是产生了一对共轭极点,具体原因请求大牛指导,你的这个架构有paper吗

這電路架構是paper的

也用過哦

不應該這麼差唷

这架构仿出来就是这样 一对共轭极点

,两个极点贴一起了。咱就不能把电路搞的简单点么?

Q20你用什么样的NPN?你怎么考虑他的基极电流?dropout时你的N2和N1都压的很低。你要用多大的管子才能满足dropout voltage要求?这个会吃很多静态电流把?你打算把主极点放在那?如果放在输出,你觉得Cc在不同负载下会产生那些问题?对这个电路你打算怎么做过流?直接过流上拉pmos gate?

你可以请教你们司经验丰富点的工程师帮看看。

paper的名字是?

这个运放的电容补偿方式是cascode电容补偿?

那个共轭极点,应该是复合管组成的射极输出器,驱动后面功率管gate电容引起的

小编,可能是你的补偿没做好,相位裕度不够,你要看N2极点有没有推倒带外,另外Cc的零点有没有消掉N1的极点。

http://bbs.eetop.cn/thread-438444-1-2.html(有附件)

文章说明

这结构俺也有尝试过,稳定性倒没有什么问题,致命的是VIN较低时dropout会很差,多个source follower的VGS......

复合极点的分析很复杂, 至今没看到很详尽而且令人十分信服的结果。

共轭极点会引起阶跃响应的ring

导致瞬态变差

可以列一下传输函数看一下主极点的位置。

ripple存在说明是传输函数的极点不是纯实数根,也就是存在共轭极点对,找到这个极点的位置并且调一下相应的电阻或者电容,使其有实根就好了。

这个电路其实挺常见的,但有个很大的问题就是低压应用,M7,M3,M21,MP就限制了输入电压。真是让人无奈

LDO锁相环应用比较广泛把!