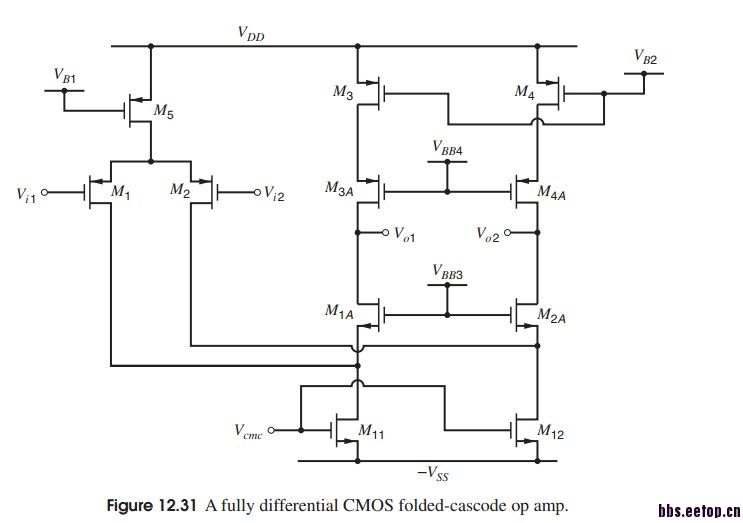

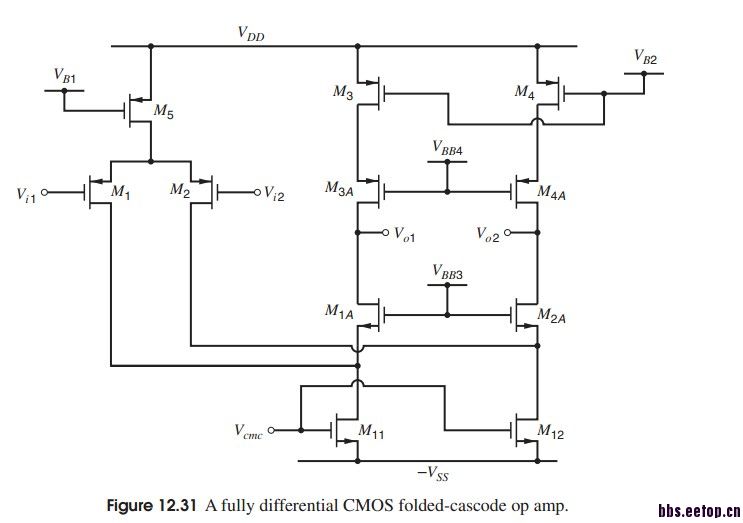

折叠式共源共栅全差分运放共模反馈输出端接哪比较好?

时间:10-02

整理:3721RD

点击:

如上图,共模反馈电路输出端可以接到M5,M4,M11的栅极

1接到M5的栅极,CMFB信号通路中极点数会比其它两种要多一个,这种方法不好。

2接到M4或M11的栅极,CMFB信号通路中属于主运放的极点只有一个,在M4A的源级或M2A的源级。若共模反馈输出端接到M11的栅级,带宽要比接到M4栅极的

大的多(nmos迁移率大),而且CMFB增益也要大(due to large gm of nmos FET).

所以最好接到M11栅极。

以上是格雷书中的解释,各位大牛,你们怎么想的啊。

接M11/M12 会有失调的问题吗?

感觉都会有失调的问题啊。

这种结构我用过 在做adc的时候 一般都是接到M11端 具体原因不清楚 反正接到M5不是好方法 也没看到有那么接的

不清楚?那你为什么选择接M11?师兄让你接M11的?

接11好。

CMFB比DF loop一般都会多个高频的pole。如果cmfb loop的bandwidth比较大,就需要额外考虑补偿

CMFB loop,这样DF loop就会over compensation,影响速度。所以,一般希望CMFB的bandwidth比

DF的小一些。如果接M4,CMFB的输入对管一般就要NMOS,意味着更大的bandwidth

学习了 谢谢jeff_zx

谢谢哈,大牛威武!哈哈

顶一个

我觉得6楼的说法有问题,应该是希望加上共模反馈后环路增益的带宽大于输入到输出的开环增益。

还有,共模输出接M5,共模输出到Vout的增益比接M4或M11更大

你讲的跟sansen正好相反,他说CMFB的GBW要高于差模的GBW比较好。

共模反馈需要接时钟信号,那时钟信号怎么接?有什么需要注意的吗?

对不起,我没能力回答你这个问题,看看有没有这方面的大牛来帮你。

顶着贴

顶一下

所以呢 结果到底是什么