泪奔吐血求帮助:spectre变压器模型(反激式开关电源拓扑)

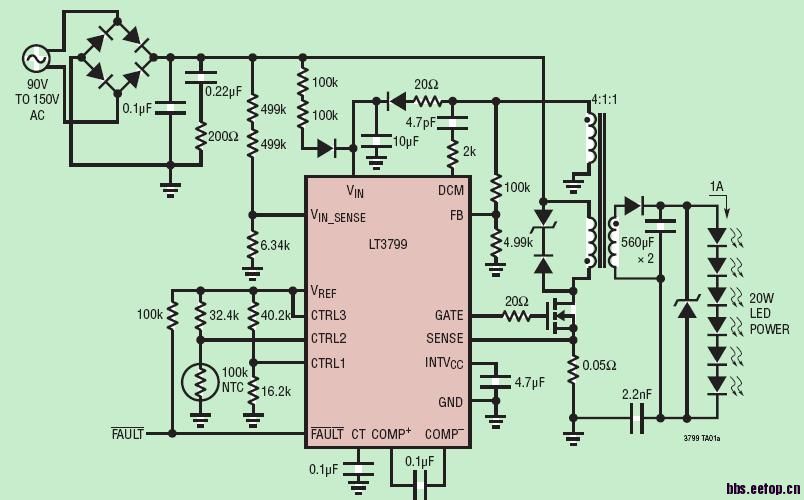

如图中三抽头变压器的spectre模型怎么实现,等效也行。

如图中三抽头变压器的spectre模型怎么实现,等效也行。反激式电路的用到的变压器有这样的特点:开关MOS管关断时,第一绕组的电流瞬间变0.第二绕组感生电压反向,电流瞬间从0变到一定值。

试过一下三种方法都不能实现第一绕组电流瞬变到0,如下三种:

1.直接用analogLib里的xfmr,这个模型应该是理想绕组吧,好奇怪的,第一绕组加一个方波电压,第一绕组电流居然也是方波,而且电流很小,是不是说xfmr模型电感很小电阻很大?结论:电流是跳变了。可是一开始就变,不是需要斜率上升的么

2.xfmr第一绕组并联电感ind。可以模拟变压器,但是仍然无法实现第一绕组电流跳变,而是通过二极管和齐纳管放电(如本帖图)。结论:不行

3.用两个电感ind,取名L1和L2,用一个analogLib里的mind耦合系数耦合两个电感。电感设置电感值和内阻(内阻很小大概几个m欧),耦合系数K1第一绕组填写L1,第二绕组填写L2,耦合系数1。还是不行,仍然无法令第一绕组电流瞬变。结论:不行

吐血泪奔跪求帮助啊

持续关注,论坛里也没找到答案。

你们要抄Linear的芯片的话,可以这样做:LTspice可以提供系统级的仿真,然后调用里面针对变压器的spice模型或者使用pspice的模型,将该模型转换成cadence的Veriloga建模.系统级方针结果和芯片方针结果做个对比。

spectre 可以CALLhspice model

另個是 callverilog-A

edaboard google 到

// VerilogA for edaboard, transformer, veriloga

`include "constants.vams"

`include "disciplines.vams"

module transformer(pr1,pr2,sec1,sec2,th1,th2);

inout pr1,pr2,sec1,sec2,th1,th2;

electrical pr1,pr2,sec1,sec2,th1,th2;

parameter real n1 = 1.0 from [1:inf); //number of turns in primary winding

parameter real n2 = 3.0 from [1:inf); //number of turns in second winding

parameter real n3 = 3.0 from [1:inf); //number of turnes in third winding

parameter real L = 1n from (0:inf); //inductanse per one turn in H

parameter real k12 = 0.97 from [0:1]; //coupling between first and second, first and third windings

parameter real R1 = 1.0 from [0:inf); //resistance of primary winding in Ohm

parameter real R2 = 3.0 from [0:inf); //resistance of second winding in Ohm

parameter real R3 = 3.0 from [0:inf); //resistance of third winding in Ohm

real k13,F1,F2,F3;

analog begin

@(initial_step or initial_step("dc")) begin

k13 = k12;

end

F1 = L*(n1*I(pr1,pr2)-k12*n2*I(sec1,sec2)-k13*n3*I(th1,th2)); //magnetic flow through primary winding

F2 = L*(n2*I(sec1,sec2)-k12*n1*I(pr1,pr2)+n3*I(th1,th2)); //magnetic flow through secondary winding

F3 = L*(n3*I(th1,th2)-k13*n1*I(pr1,pr2)+n2*I(sec1,sec2)); //magnetic flow through secondary winding

V(pr1,pr2)<+R1*I(pr1,pr2)+n1*ddt(F1);

V(sec1,sec2)<+R2*I(sec1,sec2)+n2*ddt(F2);

V(th1,th2)<+R3*I(th1,th2)+n3*ddt(F3);

end

endmodule

查看了LTspice的网表,这样的变压器只用4句话搞定:

L1 N001 N016 400μ

L2 0 N005 25μ

L3 0 N008 25μ

K1 L1 L2 L3 1.

这完全就是Hspice的网表格式。于是我泪奔了。因为我查了spectre生成的网表,除了格式不一样几乎是一样的。就是没办法用

好强大的四楼。能不能瞬变指点下如何call hspice module 和call VerilogA module

HOW to use spice in spectre

http://eda.engineering.wustl.edu/wiki/index.php/How_to_use_SPICE_models_in_Spectre

Try

msic.ee.ncu.edu.tw/course/8/中央大%20學Spectre教學.pdf

I only use spice

not spectre

小编我来了。再次郑重感谢peterlin2010同志,帮助我解决了三抽头变压器的问题。这段veriloga语言描写的变压器确实很好用很方便。而且第二,第三绕组和第一绕组是反向的,更方便连线。我的系统已经顺利仿真完了

小编能细说一下怎样用那段veriloga语言进行系统仿真的吗?多谢了啊 ,我现在也正在弄一个ACDC,但还是没能搞懂反激变压器怎么仿真 ,再次谢过啦!

抱歉,我都忘了还有这个帖子了。我马上回答。

首先,反激变压器的工作原理你要先查书。

这里描述如何根据四楼大神贴的Verilog A代码做一个好用的三抽头变压器模型出来。如图1

图1,左半边是打开的symbol,右半边是放进原理图里的效果

步骤:

1.在你的工作库下选择File->New->Cell View,出现一个对话框,在Tools栏选择VerilogA-Editor,如图2

图2

2.把神四楼的代码贴进去,保存,(这里的编辑器是VI,我不会用)关掉,会收到一个提示,要不要建立symbol。选是

3.对默认的symbol进行修改,可以改成图1那样(我从从analogLib里的xfmr复制过来,好看)

4.注意极性。pr1和sec2,th2的极性相同。pr1和sec1极性相反,所以如图1那样设置是ok的。已经测试过了。

发现错误的同学回帖留言谢谢

多谢小编热心帮忙 ,前段日子回家才看到您的回复,明天好好研究试试,再次多谢啦!

感谢小编,感谢四楼,刚才在虚拟机上做了一下能够把symbol生成了,再次谢过大家!

小编你是这个芯片设计好之后,仿真整体的时候用这个变压器的吗

在做第二步的时候,我怎么不能粘贴代码呢?怎么编辑探出来的文件呢,我找到所建立 veriloga.va文件,直接把那段代码复制进去了,这时候怎么让代码去生成symbol阿?

手动去建symbol肯定跟代码没有关联关系了阿

热心的大虾,还有事请教,我用那个代码生成symbol然后修改了匝数比和电阻R跑了一下,为什么电压不按匝数比变化啊,虽然极性却是是反的,怎么回事呢?那个匝数比和电阻R可以随意设置吗,多谢指教了!

请教fu5673921 ,如何使用hspiceD调用此transformer的model,灰常感谢

请教fu5673921 ,如何使用hspiceD调用此transformer的model,灰常感谢

注意到有个小下拉框,下拉,选veriloga,才能看到设置电感量的框框。如图。各个绕组匝数需要设置,自己查电感比和匝数比的关系,每圈的电感值也需要设置,电阻值是寄生电阻。

这个真不会

小编能细说一下怎样用那段veriloga语言进行系统仿真的吗?

我是用它建立一个veriloga模型。做成symbol放到电路里,然后进行一般仿真,倒是不知道什么是系统仿真呢。你能解释一下么。

你好,请问我设计的IC有一个零电流检测功能,所以需要变压器的th1端在电感电流降为零时降为零或者负值,应该如何修改model?

谢谢!

此帖应加精

零电流检测跟model没有关系,变压器模型网上有很多资料的,可查!

您好:

看了你关于变压器建模的帖子,我现在做一个AC-DC的项目,要仿真开关管在关断的时候变压器原边的振零波形,想请教下如何在你给的veriloga代码中添加关于漏感的描述,期待你的回复!

小编,我按照你的步骤建立好模型后仿真确实有匝数比关系可是没有电感特性,我不知道是不是我仿真的问题你仿真的时候可有电感特性?还有代码中的那个电感指的是哪个线圈?

同26楼,系数k到底如何设置?

关注中!

原来极性是反的~~~仔细看了源文件才知道~~~

有问题请教,我的cadence 软件没有CDF view的下拉框,请问是否知道是什么问题,而且我仿真时netlist也无法descent到veriloga? 请帮忙指点?