LDO后仿和前仿Vdrop差别过大

小弟最近在设计LDO时遇到了一些问题,因为第一次做,很多地方不是太懂,希望做过的大牛能指点指点小弟,手动抱拳感谢!

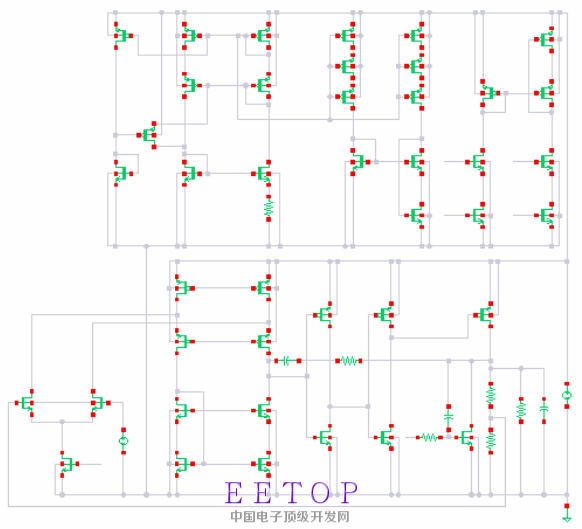

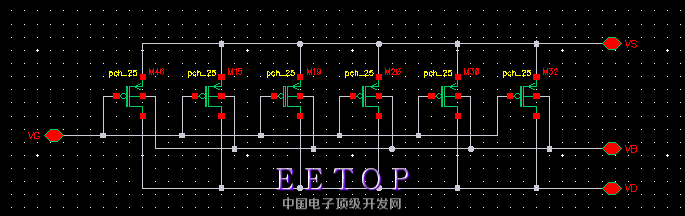

做的是一个1.8V输出,Imax=200mA,Vdrop=200mV(起码设计时是这样。)的LDO,电路图如下。上一层是偏置电路。下一层左边是EA,后面接了一个2反相器构成的buffer,之后就是输出管。

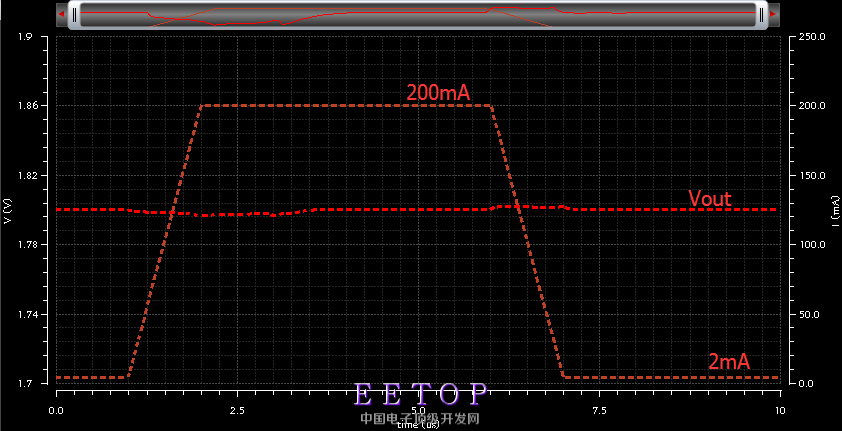

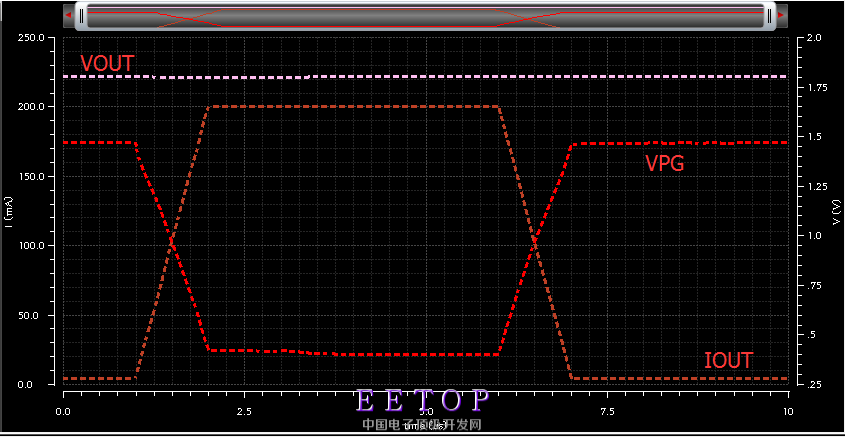

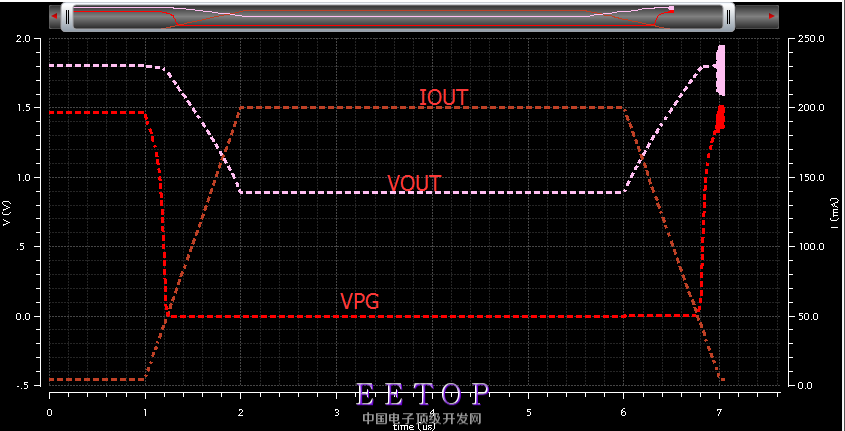

瞬态仿真结果都还可以,如下(Vin=2V),Vdrop也可以达到200mV。

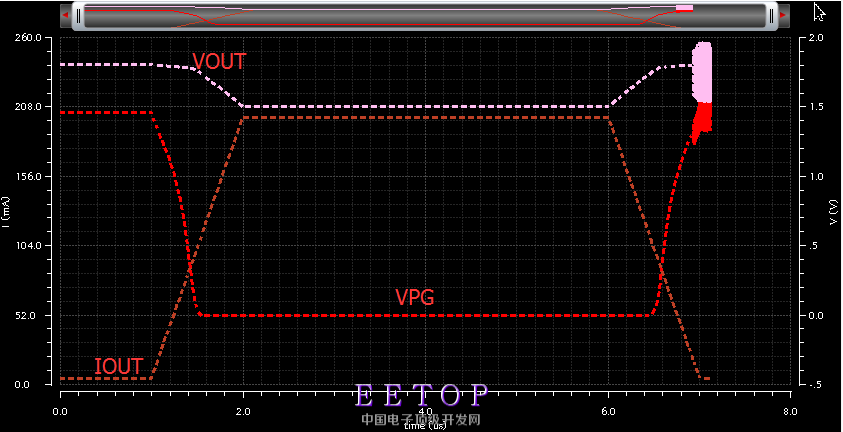

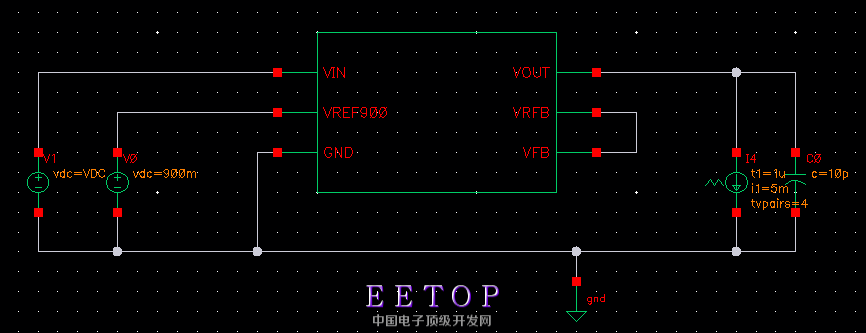

但是当画完版图后,提取寄生后做后仿发现,结果和前仿的差距很大,如下图,是输入为2V时的瞬态仿真结果。

当输出电流达到200mA时,输出电压跌落了好多,并且当输出变回到2mA时还震荡了。(设计中用的输出pass pmos 的尺寸为4800u/280n,用的是pch_25,工艺是TSMC65nm)

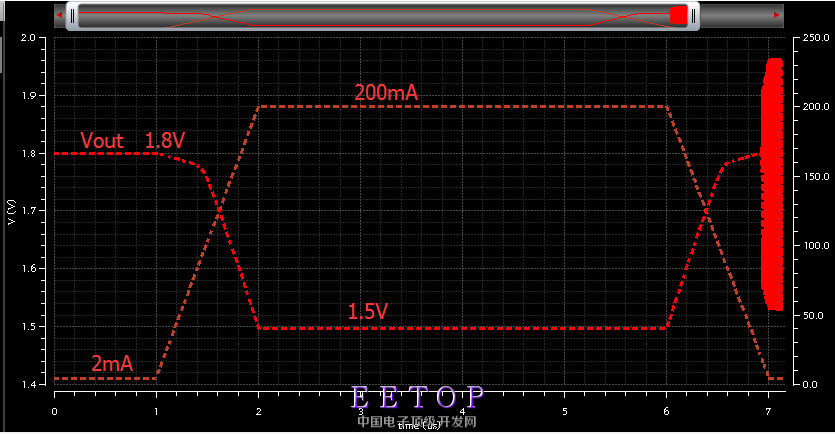

我又增大了VIN进行了仿真,发现增大VIN确实可以使输出电压跌落变小,当VIN增大到2.4V时,输出瞬态仿真结果如下。

实在是搞不清楚为什么原理图仿真会和版图仿真结果差别这么大。我把环路中的偏置部分和误差放大器部分都分别提了寄生跑了仿真发现在2V下工作都没问题。

我又想是不是输出pmos太小了,所以又把输出pmos扩大了一倍,又改了版图又仿,发现输出也没有改善,反而在电流为200mA时电压跌到了50mV?

小弟实在是很懵逼啊,找不到到底哪里出了问题,希望做过的牛牛能指点一下,手动鞠躬!

检查提出来的寄生对不对cellmap是否正确在电路中多打几个pin这样便于在画完版图后 也可以观察各个节点的电压

1.mismatch导致ea输出不对

2.ea输出高阻节点寄生电容过大

3.buffer驱动不够

想到的就这3个方向,而且图一个都看不到

可能是输出功率管版图串联寄生电阻大,你试试前仿和后仿的功率管导通电阻看是否有明显变化

瞬态。直流呢?

版图能不能放?Vin的pad之后有没有加电阻?

前仿后仿差别特别大甚至完全不一致的话,可能的考虑方向之一是版图后提的电路是否正确。后仿是如何做的,是提取成网表还是生成calibreview?两种方法都可以去仔细查看一下网表或calibreview中提取出来的的器件参数与原电路对应的器件参数是否一致。有一个可行的验证的办法就是版图后提时通过设置把所有寄生(R+C+CC)全部忽略不提,相当于只提原始电路的器件,如果提取的正确的话就是和原始电路图是一致的,仿真时结果应该是一致的,如果这样提取后后仿结果仍然和前仿差距很大,说明提取的网表有问题。以前遇到过的情况就是提取版图时,经常因为一些设置导致后提网表或生成的calibreview有问题,特别是生成calibreview要保存时弹出的窗口里要选的cellmap文件及路径、要添加finger=1以及一些要勾选或不勾选的设置等等之类的极易导致出错。上述意见仅供参考,由于您贴的图都挂了看不到,所以暂不能去分析电路设计的问题了。

这个电路我没看懂是怎么稳定的

感谢楼上的各位的回复,失效的图也已经补发了,之前发完帖子显示一直在审核所以没能及时确认。

还有我确实没有跑pass原件的直流,按照楼上说的跑了一遍。

我的输出管是6个40finger的管子并联成的,如下图

跑原理图的直流的时候,发现在输出电流总共为200mA时,每个管子的ron(ohm)=5.926,而工作区域竟然在1!

我又提参后跑了一遍,ron(ohm)=5.4,region也是1!

难道是我的输出电流小了?或是P管并联的太多了?

感谢回复,我按照你说的方法在calibre的时候不选R+C+CC,选“no R/C”又提了一次寄生。结果是一样的,应该不是提寄生的问题

这个电路不稳定吧,先把它搞正常了再说。

第一次见到反相器做的buffer拿来这么用

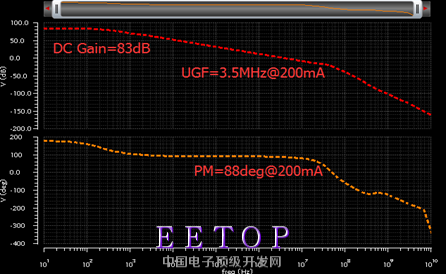

原理图仿真时稳定的,小电流和大电流输出时都是稳定的,PM有七八十度,GM有-30db左右

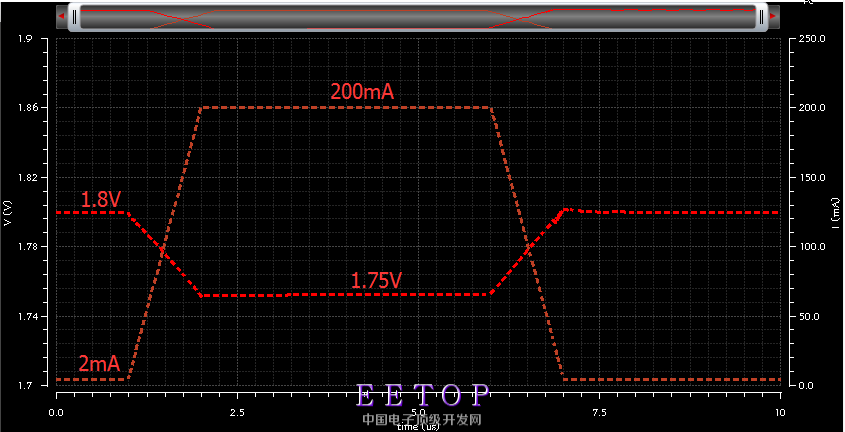

按照楼上说的那样,我又看了输出pass管的栅极电压变化,下图是原理图仿真时的trans,VPG是输出P管的栅极电压。

在输出为200mA时VPG也有个500mV左右。但是我又仿了带寄生的后,发现VPG竟然变到了0V,如下图

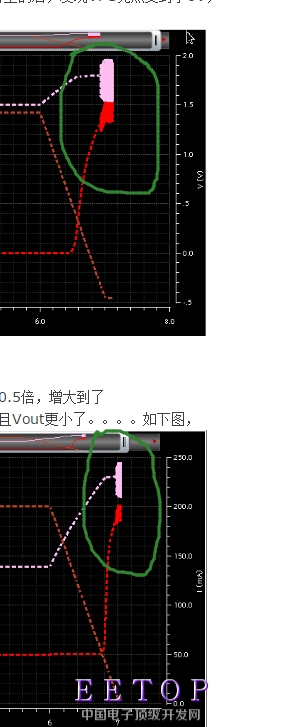

我以为是输出PMOS的电流输出能力不够,就把管子的数量加了0.5倍,增大到了7200um/280nm,然而后仿出来的结果还是VPG变到了0,而且Vout更小了。如下图,

实在不知道该怎么弄了

没人怀疑小编前仿真结果是否有误吗?

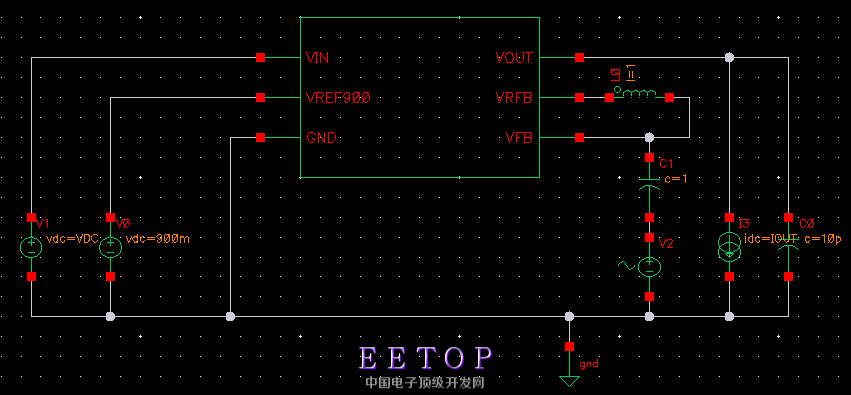

我的ac仿真是这样做的

trans仿真是这样做的

看前仿真结果,LDO输出variation在2mA与200mA 负载下在8mV以内。感觉这个结果不靠谱- -

好吧,这么一说我也感觉有点。但是到底哪里出了问题呢。

可使用排除的方法,将LDO拆分为EA和功率管两部分分别做lvs,然后前仿的EA+提取参数的功率管仿真,这样排除下就能找出原因

今天看到电路图了,11楼已经说了症结所在了,没有拿两个反相器来做LDO的buffer用的,你这个电路确实有点献丑了啊!交流稳定性仿真只能代表在此仿真条件下直流工作点处的交流是稳定的,仅仅是电路瞬态稳定的一个必要条件而非充分条件,我好像以前回帖也提到过,从仿真角度来看,交流稳定则电路不一定稳定,交流不稳定则电路一定不稳定。也请看看buffer的原理和设计吧

提no RCCC结果是好的还是坏的?

恩,提no R/C的结果和原理图没有提寄生的结果差不多。

谢谢回复!问题是在这里吗,那我尝试一下别的buffer看看。第一次做LDO,之前看到论文里有用过就试了一下,看仿真结果可以也就没想什么别的了。前面仿真阶段也尝试过别的buffer,我换了试试看。

谢谢大牛回复了!手动抱拳!

我做的一个250mA的LDO W/L=27000/0.6远比你这个大,你先保证了vdropout=0.2V时候,POWER MOS的工作区域在2或者浅1再跑跑看。