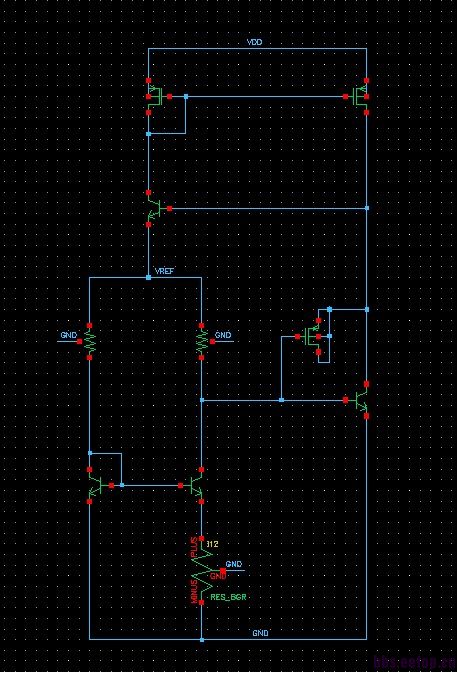

这个bandgap在如何仿真稳定性

如图,这个电路在哪里断开环路,如何加AC激励仿真稳定性呢?

Hi silverpuma:

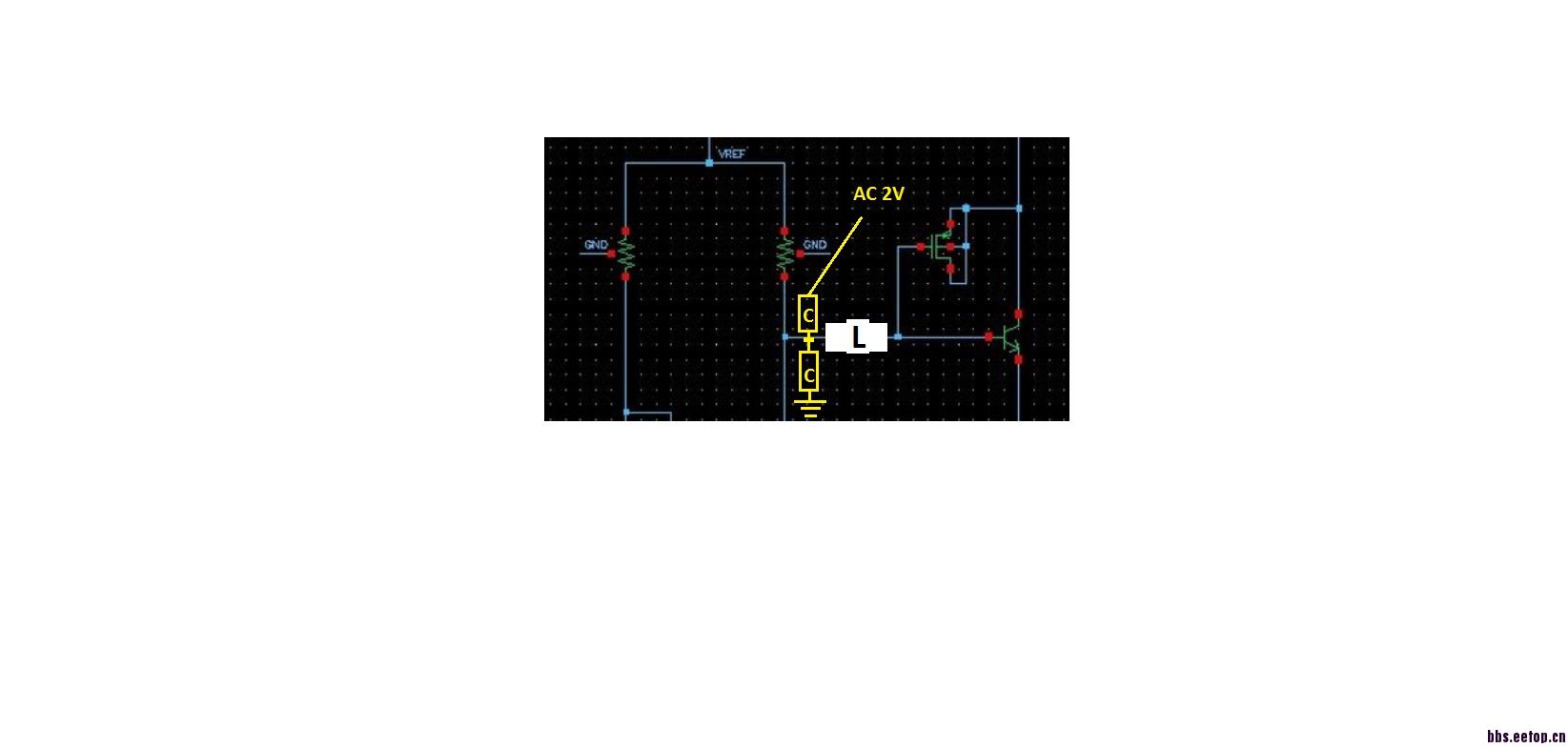

You can cut the gate of MOS Cap between R and BJT.

mpig

thanks,i can use iprobe in spectre,but how to add ac source in hspice?

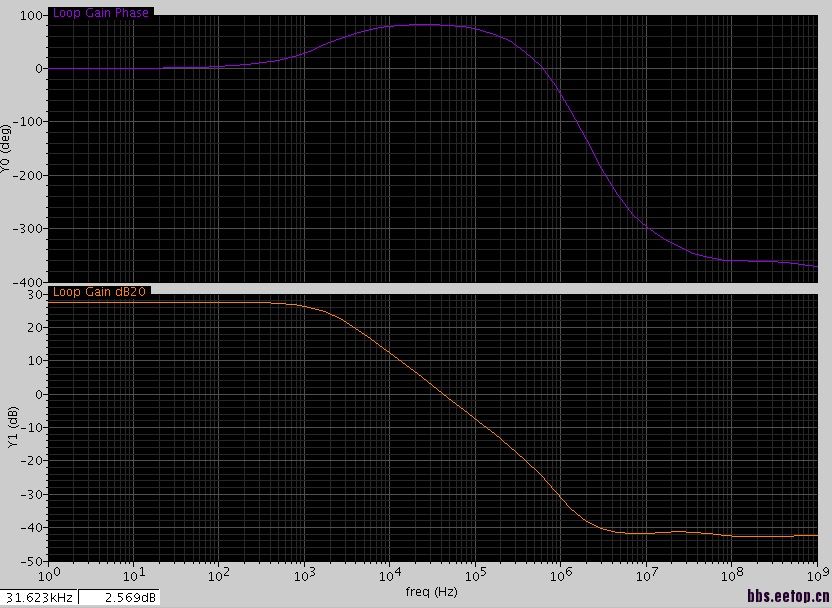

why simulation wave looks like abnormal? i use iprobe for simulation。

为啥我觉得是在上面那个npn的B极?

Hi silverpuma :

Please the attached file.

mpig

奇怪的图

HI silverpuma:

It is Strange, the loop should negative.

You can try hszgl's suggestion.

mpig

应该是上面那个NPN的B,存在两个反馈环路,在上面那个NPN的B断开,可以同时计入两个反馈环路的影响。这个电路类似于拉扎维书上的图11.23,仿真其稳定性,正确的断环点应该是在运放的输出点。

九楼正解,的确应该是从上面那个NPN的B断开仿真环路。谢谢大家的帮助。

Thanks, I also learn it.

mpig

我觉得在bjt的B端和E端断开都可以的!

因为从左往右的信号通路有两个,一个是mos电容的栅,就是一开始断的位置,还有个是电流镜的栅。而从右往左只有一个,就是上面npn的b。你可以试试在电流镜的栅上断开仿一下,把它和之前仿的结果合并,看看是不是等于断开npn的b极上的结果。

请问仿真bandgap的稳定性时为什么要断开环路?该如何找断开的位置?谢谢。