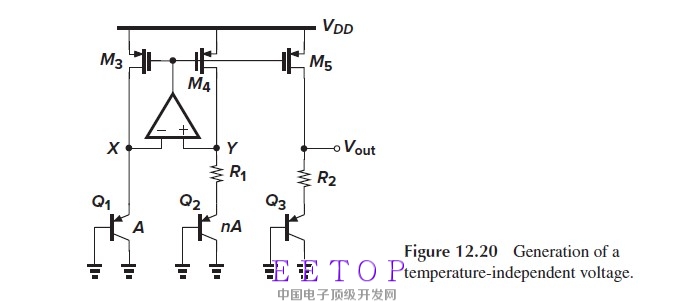

在高压工艺下,工程应用是怎么处理带隙在启动时候的毛刺尖峰?

?

这个电路的毛刺在DC扫描的时候会出现吗,如果是这样的话加电容是不起作用的,一般的结构即使有过冲,也是幅度不大的

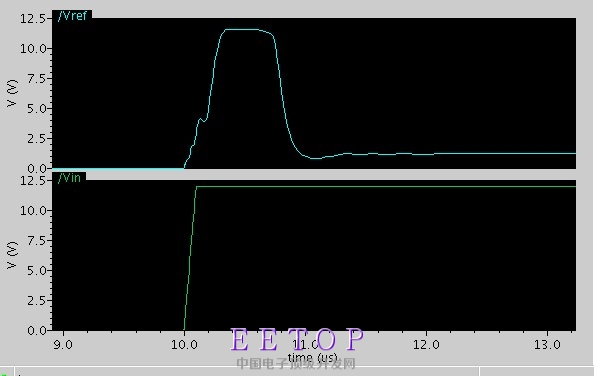

横坐标是time(us)

一般管子的耐压能力是其适用电压+50%,11V的过冲有两种原因:1是上电耦合过来的,这是上电过快导致的,脉宽一般比较小,用电容效果比较好;2是Bandgap的EA启动速度太慢,用电容也会有效果,但是根本问题没有解决。你的图上脉宽将近1us,太夸张了,应该是第二种情况,检查下EA的启动时间。

对后续管子来说,主要看管子的耐压能力了,PCM文件上有。懒得查的话,可以认为一般是额定电压+50%,5V的管子耐压一般不超过8V。

V输入不能以纳秒开始。 否则,它将通过电容耦合拉每个节点。 你的模拟是不现实的。 设置输入V启动在100usec(作为示例)。

问题解决了!我这里本质上是EA建立慢了,电路的某个点偏置没有做好,导致建立的某个时候有一个大电流给CL充电,所以过冲才这么大;如果上电太快太快了,没办法的时候只有加电容咯,正常情况下还是不额外加了。感谢指教!

DC扫的时候肯定不会有咯。我做Buck DC-DC的,有空还要多多请教你哦

跑tran的时候,啥时候开始上电并没有影响吧?影响的最主要是上电快慢(rise time),我只是好奇工程应用中,上电一般能有多快?还是说对于一个实际的应用设计,快上电和慢上电都要跑?个人觉得,如果快上电OK,慢上电一般不会有问题

最好确认一下你如何power on,如果是上电就开始,上电速度一般在100us到100ms这个水平,你这个上电仿真毫无意义,包括过冲。

另外, 如果上电是寄存器enable,那就是1us级别了, 你需要降低的你的启动电路的驱动能力。

加 soft-start 電路, 或是 voltage clamp 吧

现实或物理是重要的考虑。 过度设计是一种浪费。

VDD具有引脚电感和大面积,因此是一个大电容。 VDD不能快速移动。 从寄生提取(或至少从全芯片调料文件)可以找到VDD电容。 知道VDD引脚电感,可以计算出VDD(上升时间)最快的VDD上升时间。

ea建立速度过慢是有问题的,1us脉宽接近VDD的过冲接对于spike的响应容易失效。

嗯嗯,我上次面试也被面试官说overdesign了,符合实际需求,恰到好处的设计算是一种好的设计理念。至于后边怎么算最快的上升时间,估计我得验证验证才能明白。