PLL中分频器的相位噪声仿真

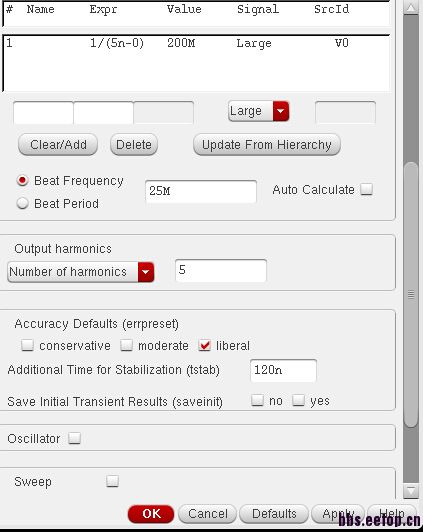

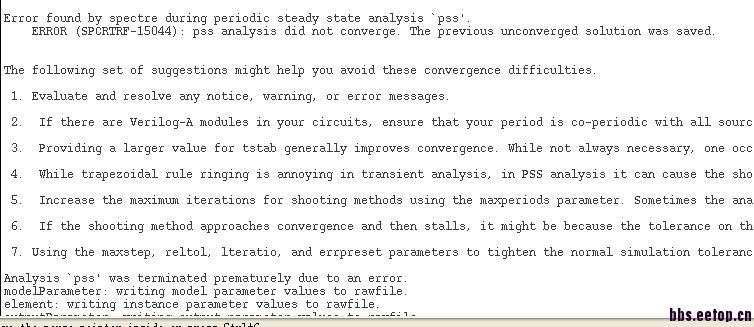

用PSS+PNOISE,PSS设置如下图:可是PSS分析始终不收敛,如第二张图所示,不知道是我PSS设置的有问题?还是本身的方法错误?,求解答!不胜感激!

你观测的频率必须是您参考频率的整数倍才可以,也就是200*i(i=1,2,......)

您好,谢谢您的建议,我这个是分频器,输出频率肯定是整数倍减小的,怎么会倍频呢?那个Beat Frequency意思应该指的就是输出频率的目标频率吧? 您做过这个模块的相位噪声仿真吗,还望给点指点,谢谢

你的PSS设置是对的,但是你的pnoise设置呢?

要想仿真PNOISE,必须得PSS先收敛才行啊,可是PSS就是不收敛,那再设置PNOISE也没有意义啊,关键是现在PSS都过不了,你仿过分频器模块的相位噪声吗?

是的,有仿真过!

Beat Frequency处应该填目标频率。关键是分频器输入源采用理想vco来提供输入信号,其余仿真按vco的phase noise分析来设置就可以。

您好,感谢您的回答,我输入频率200M,8分频,那目标频率就是25M 咯?

理想VCO模型Cadence库里面有吗?能稍微指点下在哪里可以找到吗?谢谢

在ahdlLib中,cell是vco

我找到了,是用VerilogA语言写的,但是加到分频器输入上后,PSS还是不收敛,我分频器分频系数设置为100,是不是分频太大的原因?

好像使用行为级的VCO是不能够仿真PSS的,我今天碰到了这种情况。非常奇怪

shooting和harmonic balance都不收敛吗

是的,不知怎么搞的

应该不会的。你必须保证分频器是transistor level,而不是行为级。

分频器用的是双模分频器,一个一个管子搭起来的,全电路级

我也碰到了这个问题,小编解决了吗

多等一会儿就会收敛的

请问小编,小数分频的相位噪声该怎么仿啊 Delta-Sigma 调制的

围观学习

thanks

请问小编解决了吗?pll中分频器的相位噪声应该怎么仿真呢?