LDO瞬态仿真问题

小弟最近在学习LDO设计,新手入门,就先捡了几个经典的电路尝试。但是在仿真瞬态响应的时候遇到了些问题,怎么弄都不清楚。

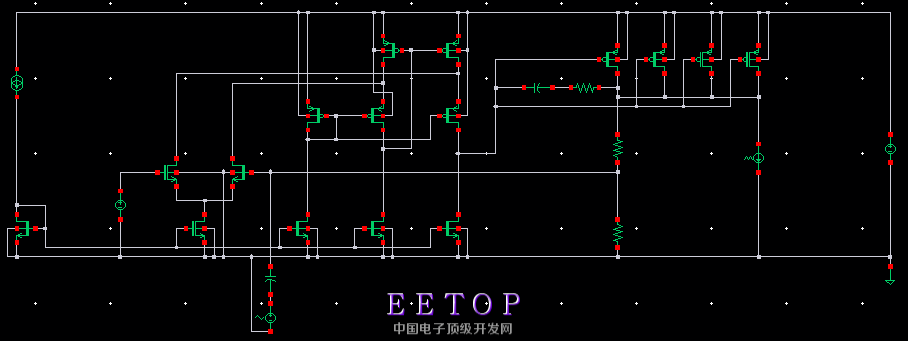

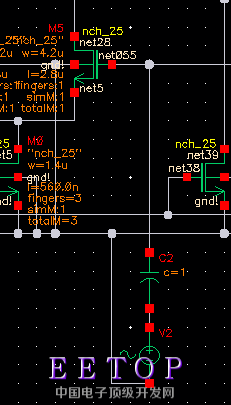

下图是仿真的LDO电路图,输入2.1V,输出1.8V,Vref为0.9V,设计输出最大50mA电流

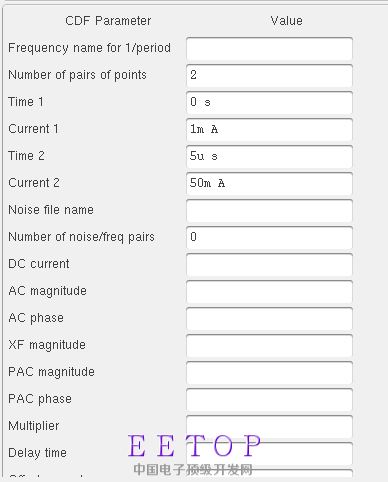

输出端接了一个Vpwl仿真瞬态响应,VPWL的配置如下图

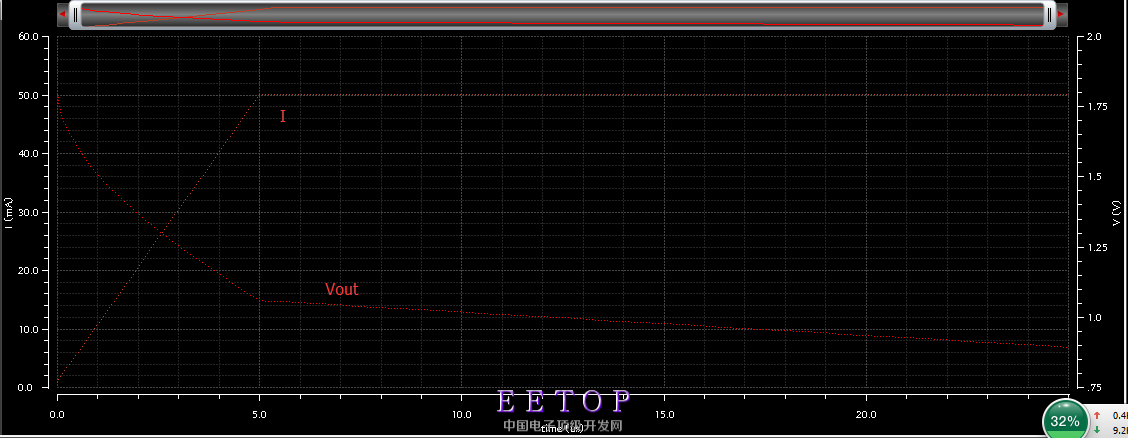

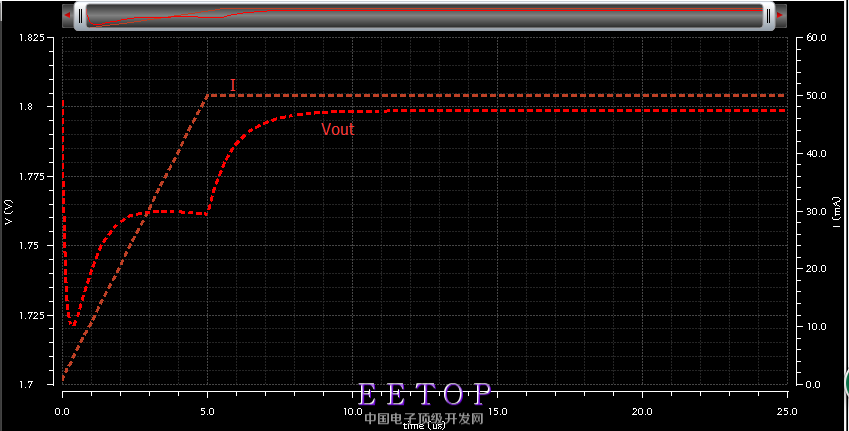

然后仿真后的输出让我很不解,如下图:

不明白问什么电压会一直跌落?即使带宽在不怎么样,输出电压也应该会回升吧,之后又延长了瞬态仿真时间,发现输出电压还是一直跌落。

然而我在仿真静态的时候,输出分别接电阻仿1mA 和50mA的时候,输出电压是准的。

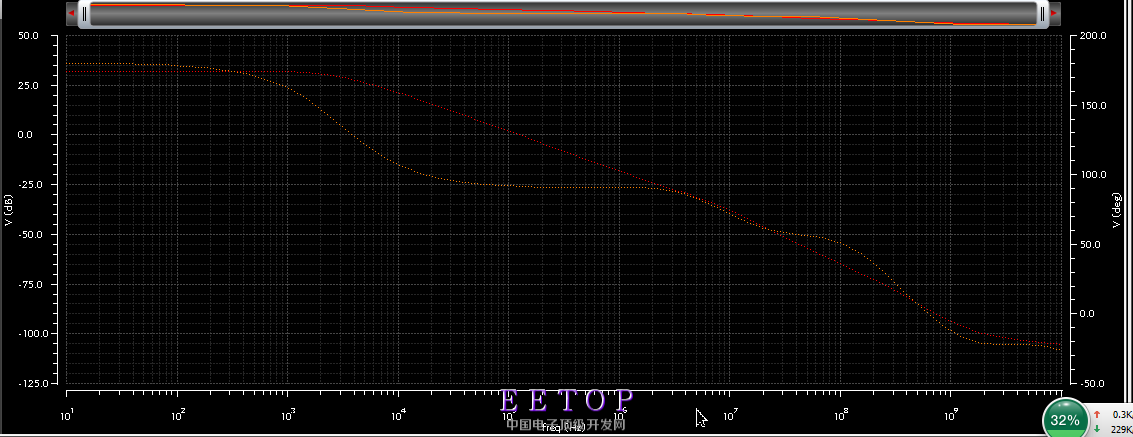

下图是增益和相移, 50mA输出时的。

不明白是我的瞬态仿真配置出了问题,还是什么其他的别的。

希望做过这块的大牛能指导一下,谢谢!

个人观点 补偿方式问题

你的电流源这样设置5us后是啥值,这样设置是你想要的吗?

差分对管另一边的电容和电压源是干什么用的

这样设置5us后就一直是保持在50mA的。

那个是用Vsin串了一个1F的电容在Vfb端,想仿真ac用的

是这种Miller补偿方式的问题吗?我也尝试了别的结构,也是用的Miller补偿,输出也会有这种电压跌落的现象,明明闭环增益还挺高的。不懂。

Vsin的幅度为不为0,不为0的话对输出没影响?

vsin我是只设了 AC magnitude 为1V, 应该是没影响的,以前仿AC时都是这么设的。刚刚也仿真了,对那个Vfb点的点位没影响的。

Iload is too large, the LDO cannot support 50mA load.

这个应该没问题好像,我也根据公式大概算了一下pass管子的尺寸,用的是pch_25,尺寸是3200u/280n

终于找到了,是那个加在Vfb端用来仿真ac的1F电容的问题,

我把上图中的电容和Vsin去掉了,输出终于正常了。虽然还要调带宽和相位。

谢谢了手动鞠躬~

接电阻输出正常,那如果接idc呢

不太清楚哪里有问题,但看波形,t=0电流刚开始增加的时候,输出就不对了

ac仿真bench错了,输出反馈接到输入端应该要加一个大电感交流断开。

谢谢大牛回复,

想问下是不是除了我加vsin的地方串个大电容到输入,输出反馈再串个大电感到输入端就可以了?

还有我做ac仿真的电路是不是不能直接用来仿trans?需要把大电容大电感那部分删掉?

小弟实再新手,望指教!谢牛牛!

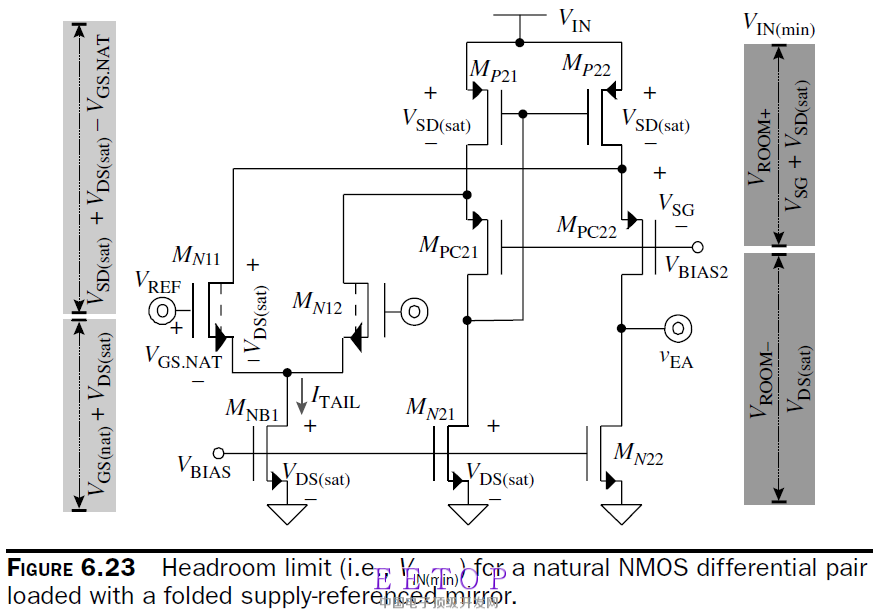

能说说你这运放镜像结构在PMOS上的原理吗?学习一下

ac的bench何乐年那本书上有啊。

我也是新手啊。我理解的是tran仿真时,ac bench的大电容相当于LDO的输出电容了,所以应该是有影响的。

没太明白你的意思啊,你是说的输入信号镜像到后面连的一个cascode上的原理?

并没有学过那本。我也觉得是,感觉不管是那个电感还是电容都会有影响的,是我XX了。

我的意思是我见过的这类运放应该在下面NMOS上做镜像啊,你这种做法的第一次见,感觉怪怪的,想请教一下原理,哈哈。

这个我觉得不影响吧,不管是在镜像的同一端加,还是另一端加,只要确保把差分电流注入到低阻端口就行了吧。我是这么觉得的。上面用的那个电路里的误差放大器是用的Rincon-Mora那本LDO设计的书里的电路,如下图

你仔细分析一下试试,看看有没有矛盾!

这个帖子里有讲到,你可以看下

http://bbs.eetop.cn/thread-389483-1-1.html

上面PASS管的宽长比小了,即使全开了也无法提供50mA的电流 所以VOUT才会下降“试图”通过增大VDS 来调节 但是还是无法稳定