关于上电复位

时间:10-02

整理:3721RD

点击:

关于上电复位,请各位大侠指点一二:

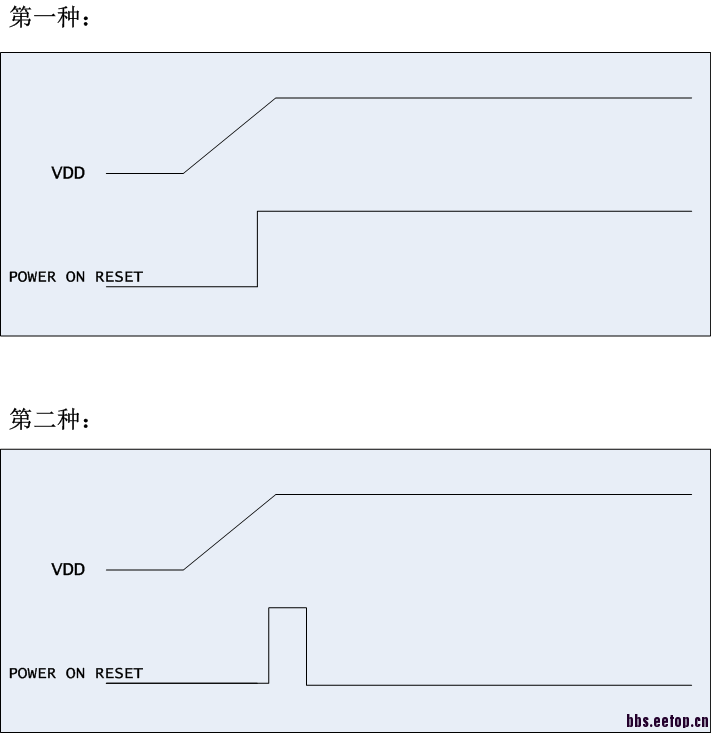

接触过两种上电复位,不知道下图两种相对有什么优缺点:

看到回帖,我需要补充,第一个是低复位,在电源上电后释放复位,第二是高电平脉冲复位,两种都是给数字模块复位用的,不必担心后面电路有效电平的要求,可以通过逻辑调整,使之适合后面的电路单元。

顶部的数字电路,模拟电路需要初始化。

底部的数字是只使用纯数字电路的脉冲可以初始化寄存器。

我用过的都是第二种,毕竟reset信号就应该只工作一次就好,一直拉着功能就不对了。

第一种是要把系统一直处于复位状态,直到复位状态被解除,系统才能进入正常工作状态。

第二种常见,供电稳定之前不需要复位,数字逻辑内部是什么状态不用关注,反正供电还没正常,系统上电稳定后再全局复位,之后数字部分就能复位到期望状态

第一种可能会出现,在vdd上电非常快的轻快下,低电平reset并没有起作用。

VDD 上升速度不同 ,2种复位电路可靠性不同

模拟模块产生第一种信号,再通过延时等数字电路产生第二种信号。

第2种用得多