为什么240MHz的运放只获得5M的转换速率?

把设计好的运放用于2.5Bit MDAC中,选择当前级Cs=3pF,Cf=1pF,下一级2Cs=1.2pF,这样运放的负载电容大概是2.5pF,仿真后发现,保持阶段的信号建立时间需要0.1us,也就是说这个运放的转换速率小于5MHz。

请问各位高手,相同的负载条件下,为什么240MHz的运放只有不到5MHz的转换速率?

(MDAC中共模反馈采用开关电容结构,Cl选择0.1pF,开关是最小尺寸)

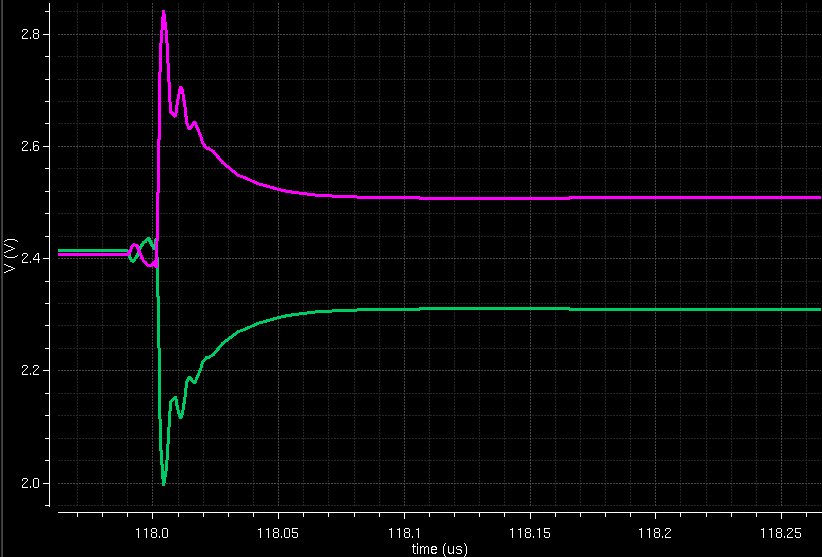

保持阶段的信号建立过程细节如下图,可以看出有较大的过冲,下降很缓慢

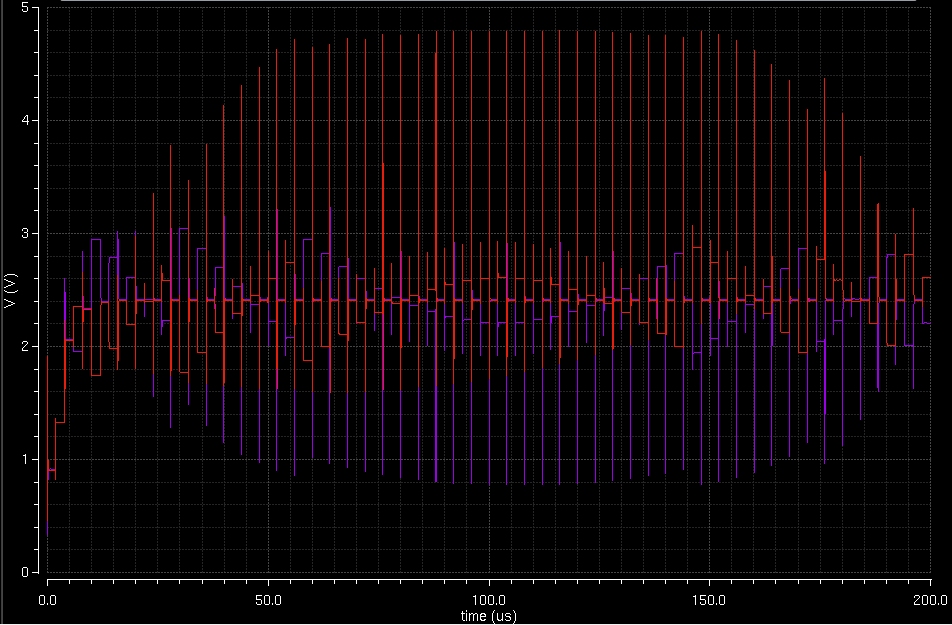

信号建立过程中还存在很多的毛刺

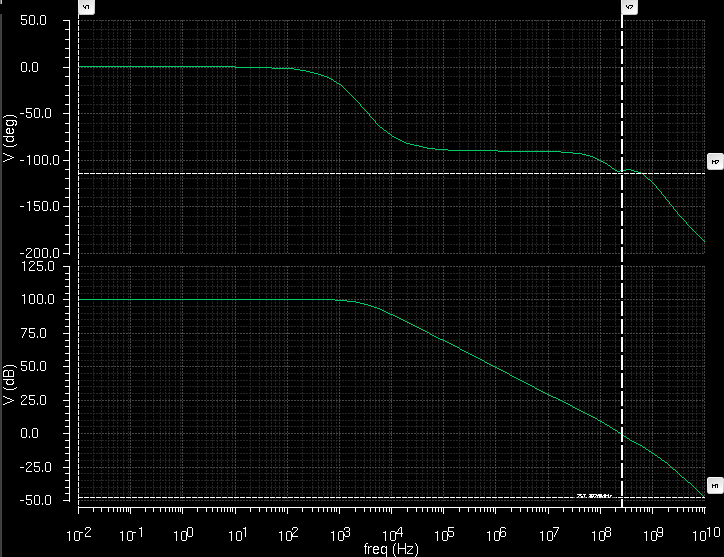

下图是差分运放的波特图

关注。

不知道哎

期待高手解答

那个5MHz的转换速率和你的250Mhz的单位增益带宽积没有关系吧,转换速率是大信号过程,只由你的输出级拉扯电流和负载电容有关,感觉转换速率不是太慢了,而是太快了,太快容易造成极大过冲,过冲应该属于正常,二阶系统稳定在30%~50%的过冲好些(纯粹从二阶系统响应考虑)

另外,从你波特图在单位增益带宽处好像有一个零极点对

请问“波特图在单位增益带宽处好像有一个零极点对”有什么负面影响吗?

个人觉得,240M的带宽只是增益带宽积,还需考虑信号增益带来的带宽降低。

另外,240M是小信号响应带宽,电容采样基本属于大信号响应了,和240M没啥关系

在零点或者极点值附近,相位变化速率是最快的(幅度的-3dB点对应相位的45度),即使一个零极点对离得很近,他们各自对相位的影响也会很明显吧,造成相位裕度比较大的波动,引起的震荡对电路的稳定时间有较大影响,所以尽量让零极点对处于GBW之外,2倍位置就应该没啥影响了

纯粹个人理解

谢谢,题目里表述有误,转换速率应该是采样速率。

根据上图的仿真结果,大信号花费的转换时间大概在5ns,其余90ns是不是属于小信号的建立时间?

这个小信号的建立时间是由闭环带宽直接决定的吗?

运放开环带宽240MHz,闭环增益是4,因此闭环带宽是60MHz,大概是16ns,按计算,应该在16ns内小信号就能建立好,但是仿真结果缺少小信号建立的非常慢,不知道哪里分析有问题?

请问这个零极点是不是由辅助运放的开环的单位增益带宽决定的?

那我增加辅助运放的输入管的Gm应该就可以把零极点往GBW外推了是吧?

您好,我也遇到类似的问题,一直没能解决 ,你的问题解决了吗?能否帮忙指点一下,我的QQ号码511644215,期待你的回复,万分感谢!

Settling time is different from bandwidth. There is a way to calculate the settling error from bandwidth, feedback factor, and input cap.

SlewRate不够

关注。

再次学习关注

转换速率和带宽没有关系,增加电流提高转换速率。带宽衡量是小信号稳定过。

看看,BUCUO