单个NMOS做开关,怎样减小阈值电压损失?

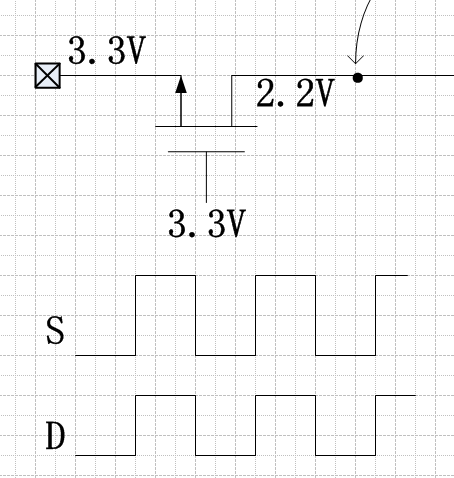

所用工艺是SMIC180的,作为对比仿真了UMC180的工艺,结果S端输入3.3V时,D端电压可以达到2.6V(满足后续电路要求)。难道是因为工艺的原因,但这差别也太大了吧?

求救求救……

注:不能使用CMOS传输门或PMOS做这个开关。

这个用chargepump自举gate

这个问题是在做IO电路时遇到的,不能花费大片面积来做自举升压。

谢谢你的回复

有DNW的话可以考虑把NMOS的Sub接到Source,降低体效应带来的阈值电压增加

可以加个很简单的升压电路 ,一个反相器加PMOS即可

提升一个Vthp?

尝试过,但还是不行。

多谢!

1.上面说的方法为什么不可以?难道3.3v就是vdd电压了?如果3.3v不是最高电压就可以。

2.nmos传输高电平本来就有电压损耗,这个也没什么好办法,你又不能用pmos

用inverter加PMOS之后,虽然Schmitt输入端电压可以达到3.3V左右,但Schmitt翻转阈值会受到正反馈的影响,项目中对VT有要求,所以不行。

可能对于VT要求低的项目该方法可用。

没明白你的意思,你的nmos开关的G和D电压都为3.3v,要想S端高于2.2v(目的想接近3.3v),那你gate的电压至少要比S端高些,只要你gate电压不受限抬上去不就可以了,比如抬到3.3+Vthp就可以;如果3.3v就是最高那就不行

谢谢分享

有native 或者nature的管子吗?有的话可以很低的Vth

1.如果有更高的电源,将开关栅极接高电源,可以让源漏电压无限接近

2.如果只有3.3V的电源,但是有native管子,用它替换原来的开关管。

3.TSMC018工艺3V的NCH管子Vth应该在0.7V左右吧,你这种应该衬偏效应导致Vth在1.1V左右,如果工艺支持,可以将B端接到S端(会增加一块mask),这样VTH在0.7V附近,输出应该在2.6V左右

4.如果以上条件均不符合,可以做一个简单升压电路,将G电压抬高一个VTH.

5.如果不能增加电路,可以考虑换工艺,找一个VTH较小的工艺

其实就那么几种方法,自举、更高的电压、pump、B和S接一起、PMOS/TG、native(会有漏电)、

13楼 14楼正解