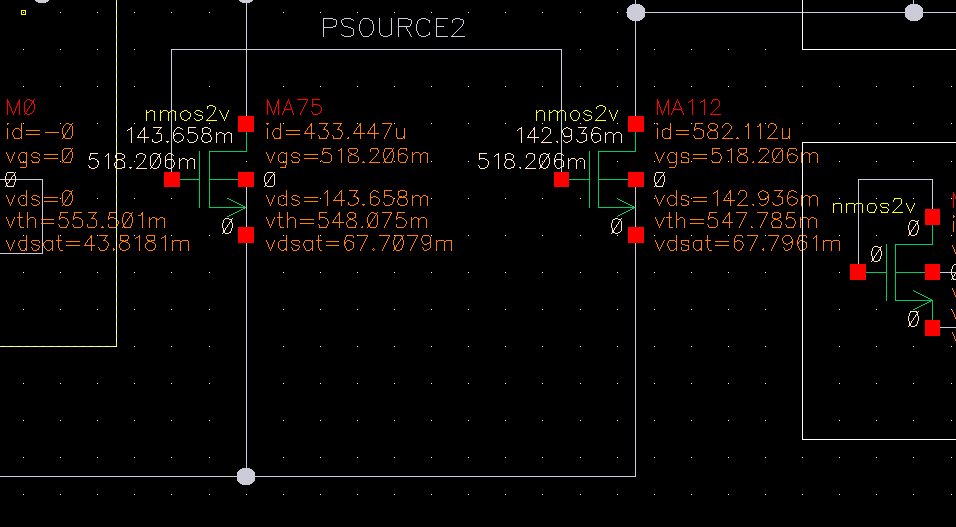

Vgs<Vth时nmos管导通了,还处于线性区的原因

不太理解为什么Vgs<Vth还能导通还有这么大的电流,看管子的状态显示的是线性区,region 3。不知道是什么原因,感觉颠覆了对模拟的认知了。

导通这么大电流显然不是图中这个MA75偏置的,MA75是被偏置的,也就是说电流应该是上面过来的。region 3应该是晶体管处于亚阈值区。

多看书吧。

region3是亚阈区region1才是线性区

vds>vdsat 饱和了电流没什么问题啊- -

管子宽长比大,偏置电流小的情况下,管子有可能进入亚阈值区域

你好,谢谢你的回复;我在网上也查了如果把Vdsat当做过驱动电压的话,那么Vds>Vdsat是应该在饱和区。那么为什么管子还是显示在亚阈值区呢。

电流会从pmos电流镜灌进来的,只是这种管子的速度稍微慢点,一般应用也不care这点速度的。

谢谢大侠回复,region3的确是亚阈值区,我弄错了。

我还有两个问题是,管子处在亚阈值区,电流可以这么大吗?我用的是0.18um的工艺。

还有设计的时候该怎么考虑考虑电流是自己产生的还是别的管子强制的呢?很关键。

谢谢大神指导

电流很大啊

电流大小是相对管子尺寸来的

根据femanxxx小编的发言如果我没有记错的话

管子在弱反型、中间反型、强反型时都可以饱和

spectre分区应该是按vgs和vth来的

你所说的饱和是载流子速度饱和吗?

说的是在这几个区的电流分别能达到最大值,再增加Vds之后Id保持变么?那么Id随着Vds在各个区里面的图像是怎样的?感觉有点晕。

还请大神不吝赐教

分清楚偏置电路和被偏置电路,你这个是被偏置的,电流应该来自上面。你看一下上面PMOS的电路结构。

VGS大于VTH为开启,但是在VTH附近时为亚阈值区域,其IV曲线呈指数关系。SPECTRE判断饱和区应该是:VDS大于VDSAT时为饱和区。注意是VDSAT而不是VGS-VTH。

嗯,谢谢指教。貌似明白了。

学习~

当Vds>Vdssat(长沟道可认为Vgs-Vth与Vdssat相等,短沟道时不等)时,管子处于饱和区,Vds是Ids的弱函数(有影响,但影响较小,一阶手工计算可以忽略,饱和电流公式有体现)。当Vgs在Vth附近,管子处于亚阈值区,Vds与Ids是指数关系。当vds<vdssat且vgs>vth,管子处于线性区,vds与Ids为线性关系。需要指出的是,实际上管子在各个区转换是平缓的过度,比如通常我们认为vgs>vth即管子导通只是便于理解。vgs在vth附近管子只是处于亚阈值区,经验上,Vgs大于vgh 50mv以上,我们认为MOS真正完全导通。再比如vds>vdssat,理论上,便认为管子处于饱和区,实际上在工程上,我们会把vgs-vth这个设为150-200mv,如果是作为纯电流源,这个值甚至会更大。以上

vdsat小于70~80mV就在亚阈值区,为了保证管子在饱和区,一般Vdsat要大于150mV,Vdsat太大了也可能进入速度饱和区。

嗯,学到了,谢谢咯

你这是哪里来的说法,,怎么感觉年代有些久远了

过驱动电压完全看要求的,速度要求高的情况下,才需要比较高的过驱动电压,不同的工艺也不一样

估计是使用的 bsim 3的模型,建议 以 vgsteff作为 设计时候的变量,具体vgstef 与 vgs -vth的关系 可以查看 bsim 3的手册

这个过驱动电压的选择,参考sansen的书,以及gm/id的设计策略

当vgs-vth>vds时,mos管处于饱和状态,此时的ids达到一个近似不变的值,但是如果外部提供的漏极电流大于mos管本身的ids时,mos管进入sub-threshold状态,以此降低漏电流。因此在设计中要注意控制该mos管上面提供电流的大小,或者增大该mos管的w/l的值以增加ids的容量

Vgs-Vth<Vds时,mos管进入饱和状态,ids近似常量,但是如果此时外部流入到mos管漏极的电流大于mos管饱和时ids的值时,mos管进入sub-threshold状态,以此降低漏电流。所以设计时应注意外部流入mos管漏极的电流不要大于mos管饱和状态时的ids,或者增大w/l以增大ids的值。

回复 19# brightorange

不久啊,就是TSMC 0.18u的工艺啊