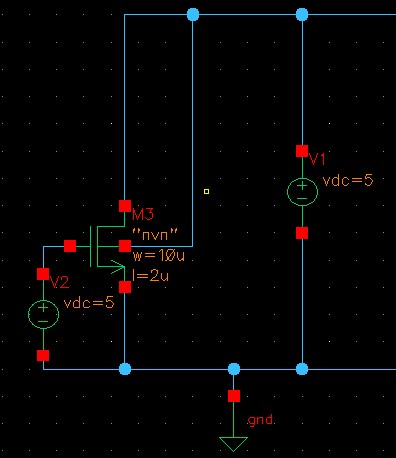

一个基础电路问题,MOS导通

时间:10-02

整理:3721RD

点击:

无意把NMOS的衬底给接到VDD

发现一个不懂的问题.

为什么Vgs>Vth时,NMOS不是导通的?

要直到V2接近VDD时NMOS才导通?

感觉很基础的,可我不会.望谁帮我解答下.

发现一个不懂的问题.

为什么Vgs>Vth时,NMOS不是导通的?

要直到V2接近VDD时NMOS才导通?

感觉很基础的,可我不会.望谁帮我解答下.

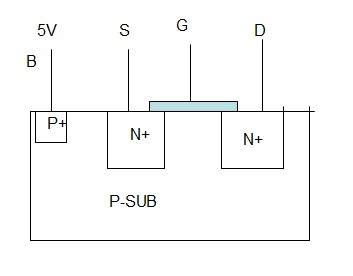

衬底接电源时,你的vgs无法使沟道形成反型层!

小编有注意到这衬底电流有多大么

现在想想,我也觉的很难形成反型层.

可为什么VG=5V时NOMS是饱和导通的?

从图中看VbsPN结应该是导通的,可VbdPN结应该是截止的

要形成反形层.VG是不是应该是5V+Vth才可以?

从仿真的结果看电流绝大部份从漏极流到衬底,这又是为什么?

毕竟VbsPN结是导通的呀.

增大管子的尺寸再试试呢?

增大尺寸有什么作用呢?

我仿了一下,变化不大.

研究哈,,,,,,,

小编,NMOS管衬底应该接地。而不应该接电源。PMOS管衬底应该接电源。

最好去看下半导体物理里的MIS结构。

小编在用Spectre啊?

我知道.......

只是我今天误接了,所以想把这个情况了解清楚一下..

同意

mosfet是靠沟道导电的,衬底接高了,就不会产生沟道了,半导体的问题

不要只研究物理结构啊,软件不是智能的,看看它的算法是不是在误接后还成立吗?

关注此贴

没这么用的。