请大神帮忙看下轨到轨运放的结构是否合理

时间:10-02

整理:3721RD

点击:

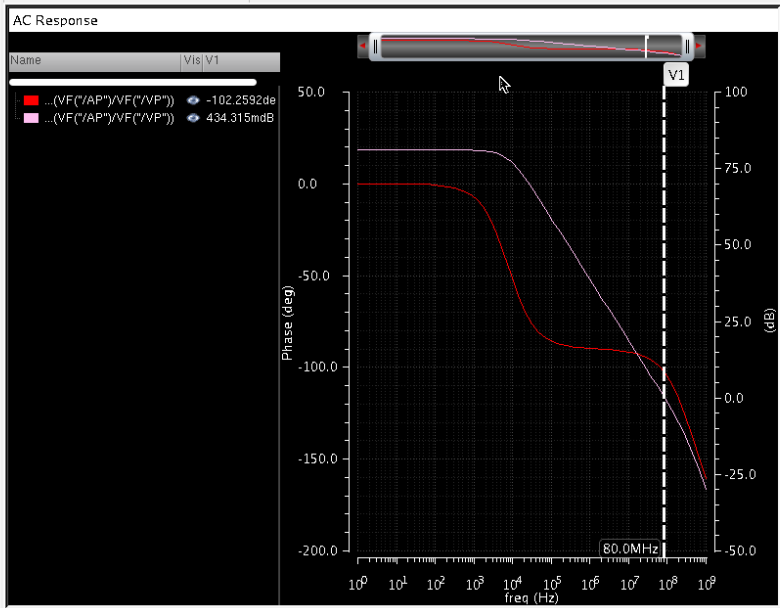

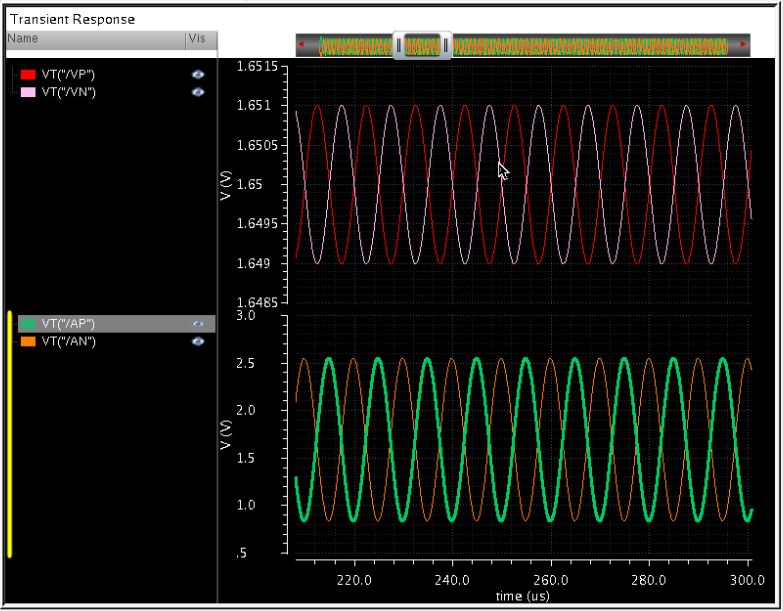

如图是现在做的一个轨到轨差分输出的运放,各项参数和输出幅度频率响应如图,奇怪的是为什么输出瞬态的相位和输入差别那么大?粗看一下,延迟125ns就是80M带宽,但是仿真结果延迟2us,为什么?

另外这是一个差分输出结构,请问单端输出的轨到轨电路会不会更常用一些?如果目的是在100KHz频率下将输入放大,应该选择单端还是双端?

请高手帮忙解答,不尽感激~

这是打算再调试的单端输出结构电路

你这个是进行的放大器开环仿真,延迟与-3dB带宽相关,而-3dB带宽俨然远小于80M,所以延迟us级正常;

至于哪种用的多,关键看应用场景,在一些高速差分系统中,多采用差分输入和差分输出;而在一些普通应用电路上,多应用单端输出

你都说了是运放了,还瞎搞。

谢谢大人~是开环仿真,在不改变负载的情况下,怎样增加-3dB带宽?

有什么建议请大神说出来,我们可以学习一下

运算放大器是不会在开环下使用的。

有人说你瞎搞还真有点那个意思

运放开环看-3dB没有太大意义,有一个叫增益带宽积的东西,等于开环增益*开环-3dB

开环增益是个不稳定的东西,受工艺电压温度变化,所以你想要的这个-3dB 的带宽会可能有几个数量级的变化

但实际中,大家并不太关心这个参数