求教,关于LDO零极点追踪的频率补偿方式

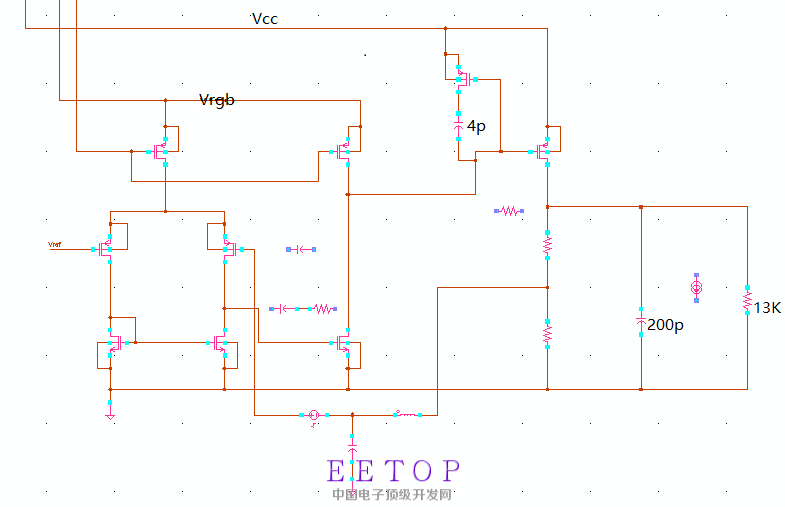

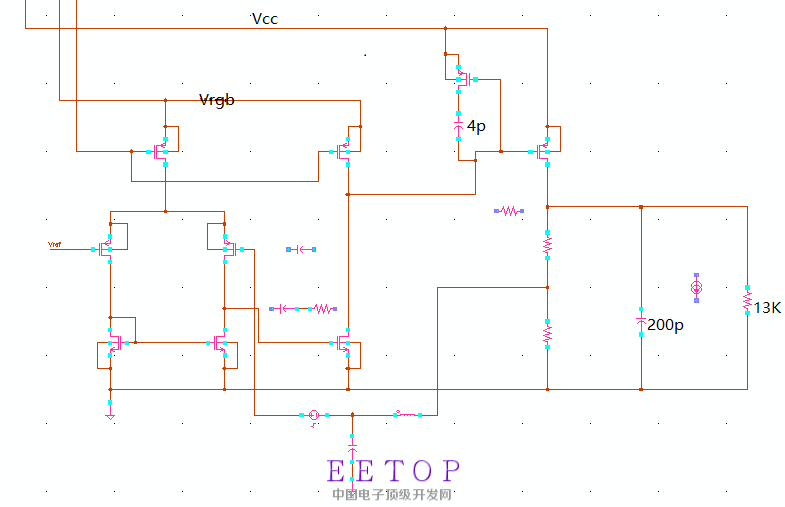

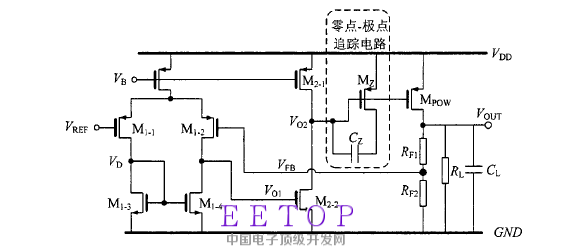

请问,是否有人用过LDO零极点追踪的频率补偿方式,为什么我添加零极点追踪电路与不添加一点区别都没有?我的CL=200p,RL为13欧姆到16k欧姆,应该如何设置如图所示的Mz、Cz?

请问,是否有人用过LDO零极点追踪的频率补偿方式,为什么我添加零极点追踪电路与不添加一点区别都没有?我的CL=200p,RL为13欧姆到16k欧姆,应该如何设置如图所示的Mz、Cz?

其中的Vrgb是前级预调整的电压,1.6V

为什么我添加零极点追踪电路与不添加一点区别都没有?

你需要大概计算了你的主次极点位置,在算你的补偿零极点位置,说到这,就牵扯你需要先确定一些其它的指标,譬如Iq,根据Iq的分配确定你的几个gm值以及ro,ci,以此为初始条件,再计算补偿的pz

每种补偿方法的效用和它引入的位置有关,太大太小都没有效果或者变坏,这都需要你先把整个电路细细算一遍,不能靠猜,靠仿。你的vcc为什么和ea的power分开了,两者是否一样,如果一样,你考虑这种搞法对psrr的影响没有?此外为什么选用这种架构,你的电路需要100dB的增益吗?你这个是三级放大器,你的补偿方式可能远远满足不了要求,增益越大级数越多对你的补偿越不利,这可能需要很大的功耗。你的200p的负载电容对应最大100mA?的负载,瞬态指标是怎么考虑的?你给的信息有限,别人没法多说

十分感谢前辈指点

EA与POMS分开供电是因为我前面的带隙基准做了电压预调整,具有较好的PSRR。所以我将Vrgb给EA,增加了EA的PSRR本来是想将Vrgb给POMS的,但是在预调整那一块已经有了个200mV,而指标要求LDO漏的失电压为200mV,100mA的负载电流,所以我将EA与PMOS分开供电。200p的负载电容是考虑版图的寄生电容

这个零极点追踪补偿方式我是看一个论文上这么用的,所以想试着做一下。

初学者,我很多都不懂,真心感谢前辈

1,好的ea的psrr不意味着好的ldo的psr,具体参见psr相关论文;

2,vrbg小于vcc,pass管可能关不断

3,负载寄生电容200p,难道是给数字供电,你做的事capless的?是否还有外接电容。两种结构的设计是不一样的。

4,请查看这个动态补偿论文的里的spec和process,这和你的有多区别,确定这个结构是否依然适用

5,做设计前必须定好spec,spec定的越全,对你设计和理解电路越有用

首先感谢前辈回答

现在在不考虑环路稳定性上,电流由100uA到120mA的时候都是正常,PMOS栅电压由1.43V到230mV变化,Vrgb为1.6V,EA应该是处于正常工作的。整个结构无片外补偿电容,对于那个负载200p是考虑整个电路版图的寄生电容(至于为什么我也不知道,导师说应当在200p左右)

我去对比下那篇资料,谢谢前辈

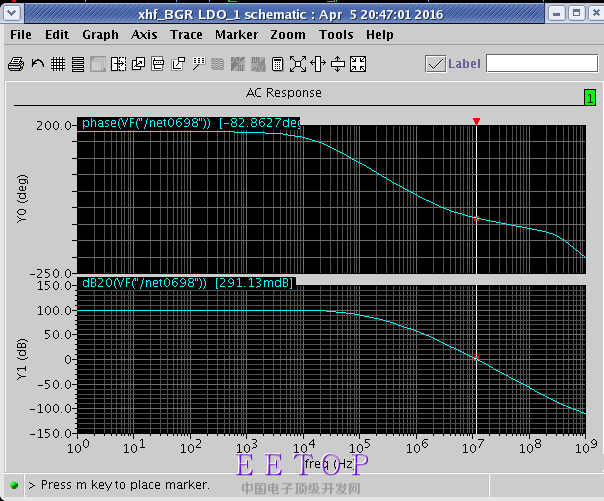

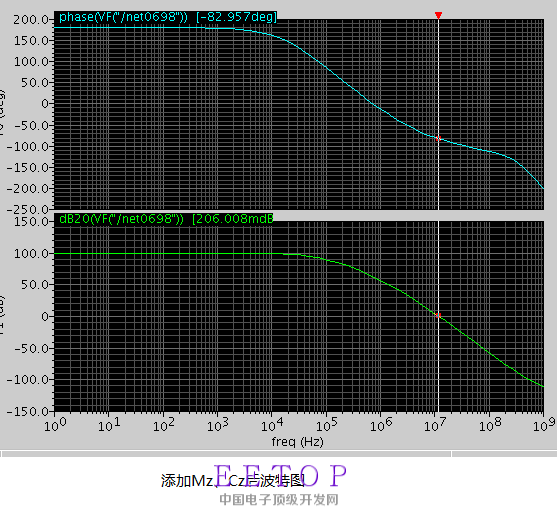

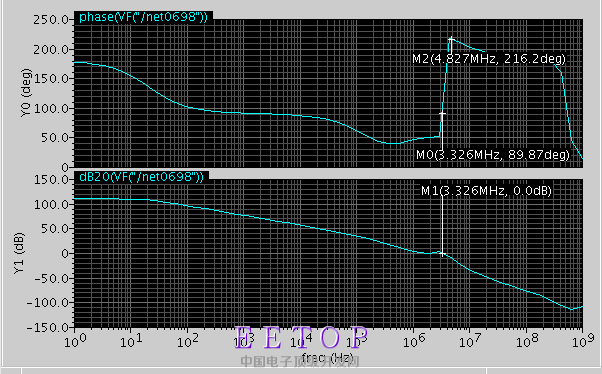

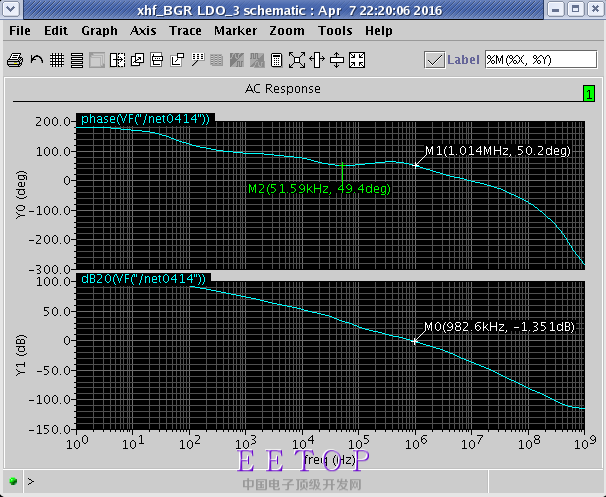

你可以把零点再往前调一点,你有两个0db的点,前一个相位裕度看起来不太够

感谢前辈指点!我将电容增加了,现在前面那个点大于了50°了请问相频后面上升了,还稳定吗?

看你的bode图是不稳定的,可能存在多个crossover point,此外,gain margin也是不够的,bode图的高频部分曲线可能和你的仿真方法有关,你可以改用stb仿真。胡乱仿真的意义不大,希望你能学会手算,把电路设计弄清楚,从简单到复杂一步步的走,譬如,先不加任何补偿,只考虑空载条件下,把电路参数设计好,确定其频率特性,步子不要迈大了,这些都是很基础的东西。

谢谢前辈,那我重新按照您说的,先进行计算一下

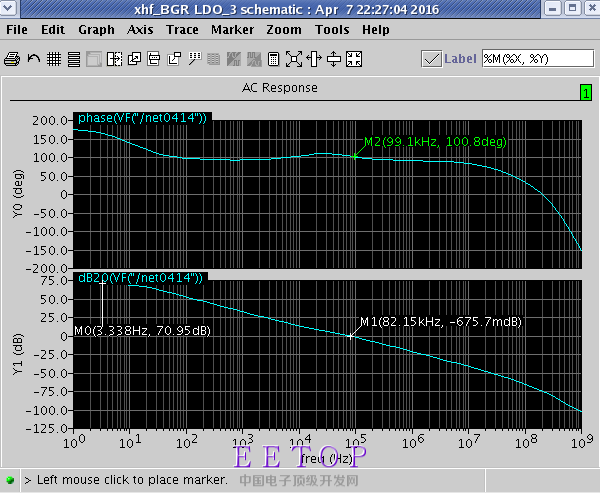

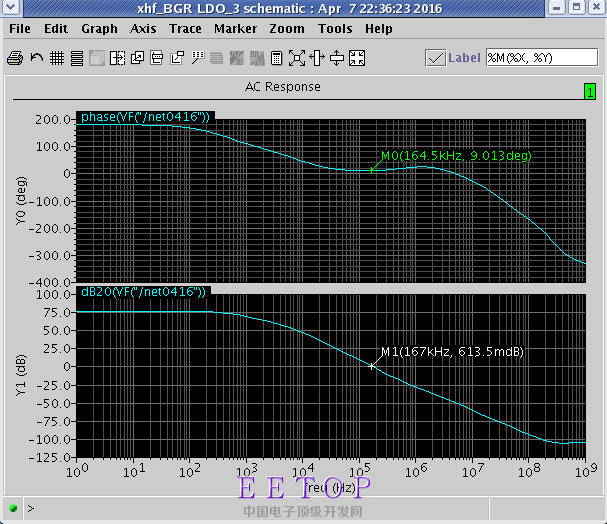

前辈,您好我大约计算了一下,然后采取了另一种补偿方式 现在在100uA到100mA是环路相位是够了 但是在空载(不接负载电阻的情况下)LDO不稳定

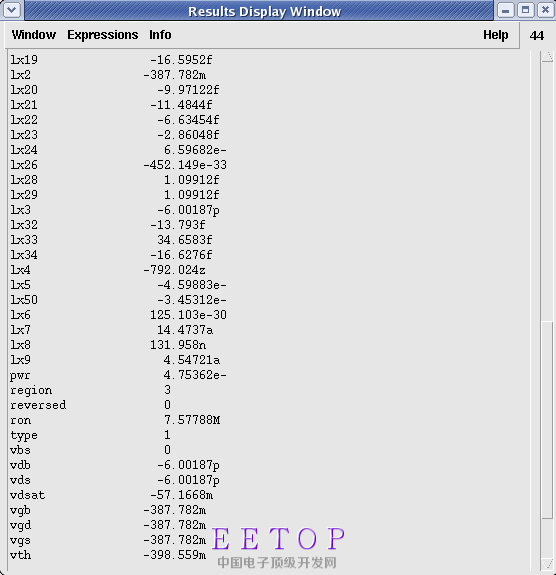

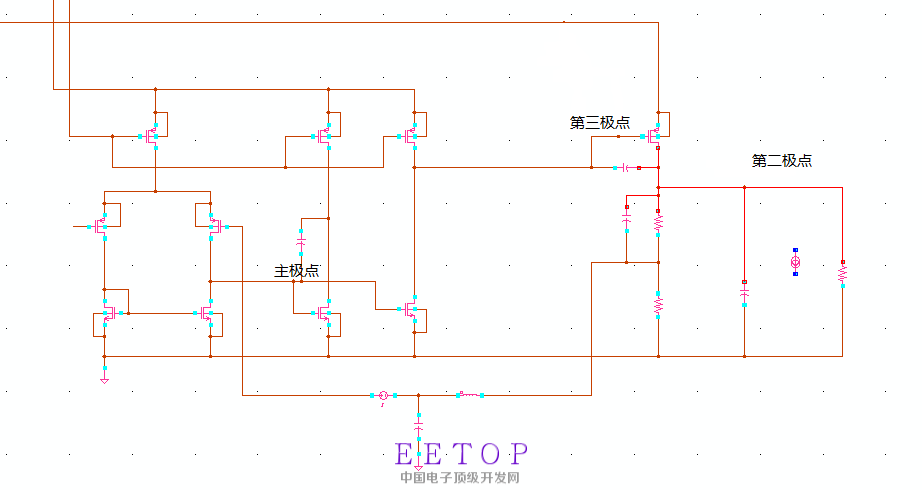

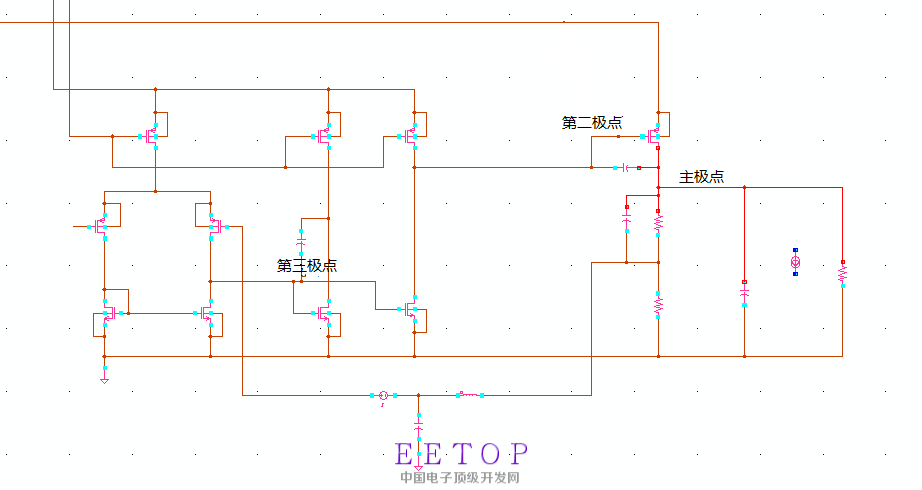

负载电流不同,第二和第三极点会发生改变我大概分析是:空载时候,调整管电流很小,由于宽长比恒定,其Vgs绝对值减小,导致栅电压抬高,调整管沟道电阻减小;栅极电压抬高,导致EA第二级不正常工作,使得第三极点处产生的零点补偿移向高频,无法抵消第二极点。图片传错了,改不过来,主极点在输出那个图

负载电流不同,第二和第三极点会发生改变我大概分析是:空载时候,调整管电流很小,由于宽长比恒定,其Vgs绝对值减小,导致栅电压抬高,调整管沟道电阻减小;栅极电压抬高,导致EA第二级不正常工作,使得第三极点处产生的零点补偿移向高频,无法抵消第二极点。图片传错了,改不过来,主极点在输出那个图请问前辈我这样分析错了吗?

谢谢分享