Cadence混合信号仿真,AMS Design Pre 编译时VHDL写的模块报错

时间:10-02

整理:3721RD

点击:

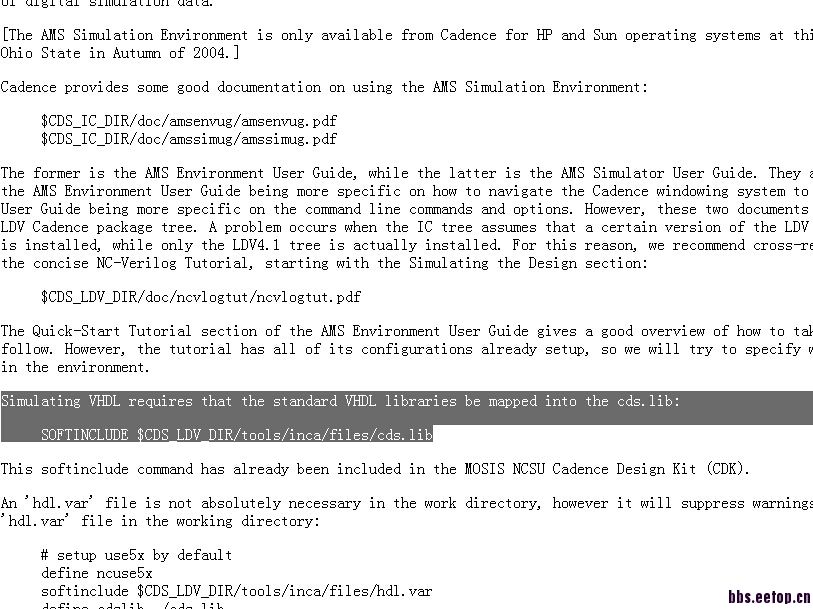

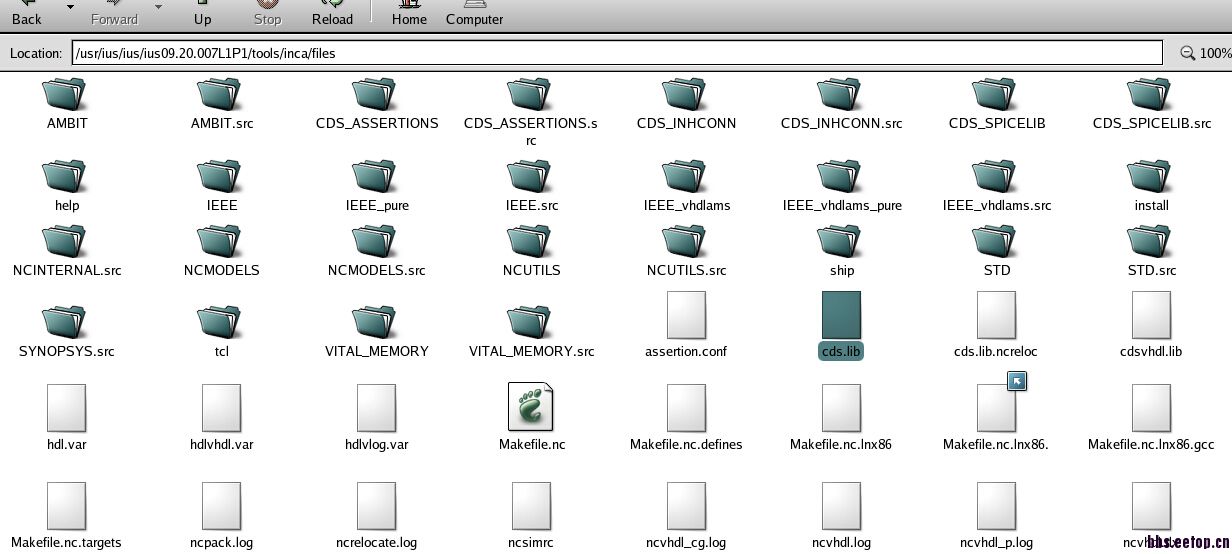

按照cadence混合信号仿真教程

里的例子学习cadence混合信号仿真。

进行到用AMS Design Pre那步时,

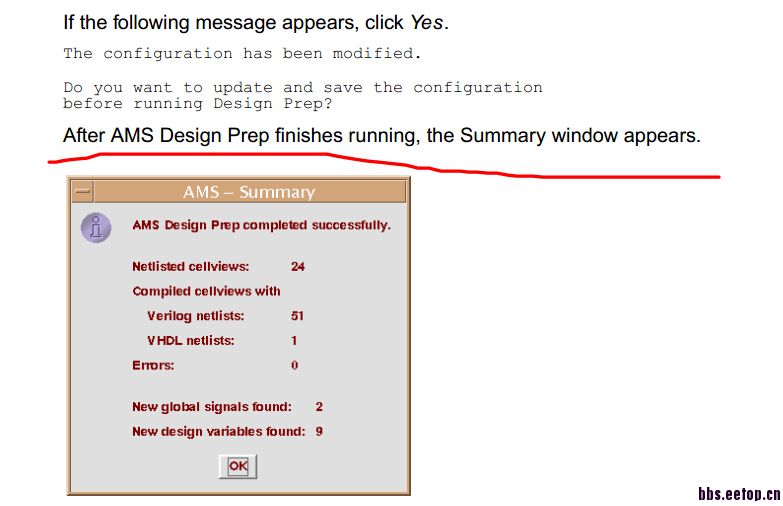

教程里 Run得到的结果是:

编译没有Eorror

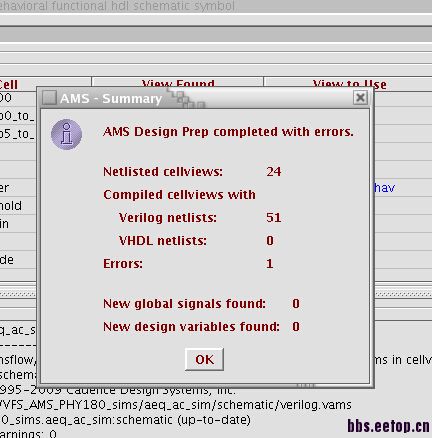

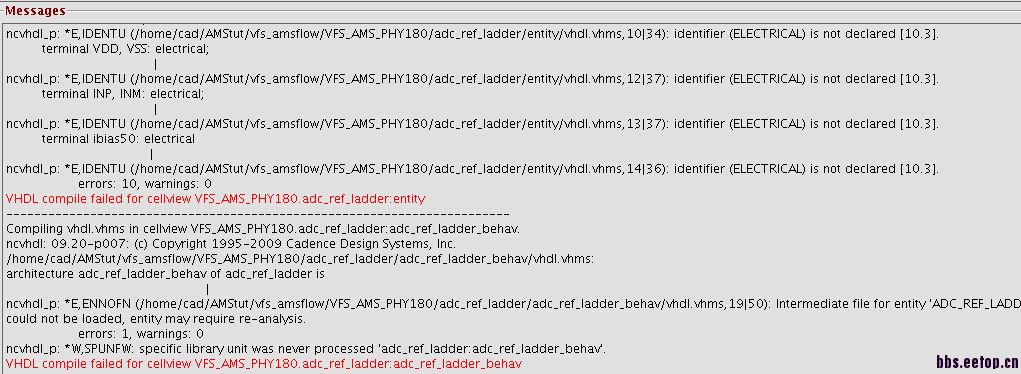

但是在我实际操作时,其中一个用VHDL编写的模块编译报错:

请问,这个错误是什么意思?

该怎么修改?

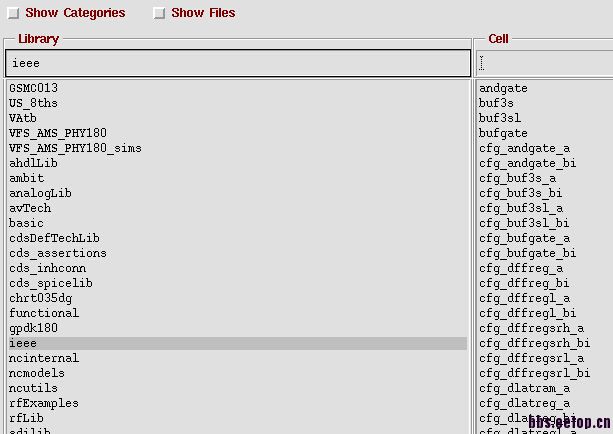

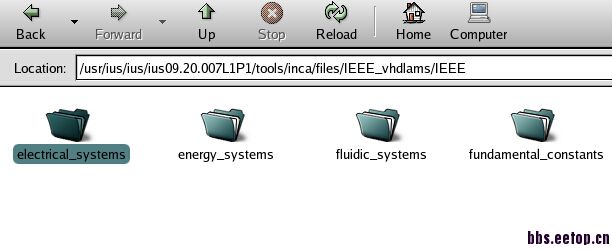

虽然知道了library ieee,std;需要添加进去,但是ieee里面没有electrical_systems这个package,在另外的文件中添加的electrical_systems的package放到ieee中,还是不行。

我在用ams进行混合仿真的时候,怎么数字部分verilog代码的位拼接结果是相反的,{}里面的左边成了低位,右边成了高位?这是什么问题啊,求大神请教!

多谢分享,正需要