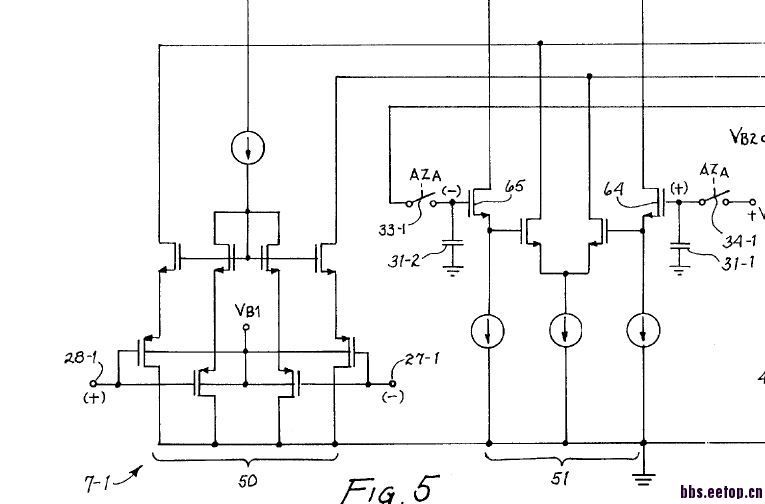

大家帮看看这种结构的输入有什么作用

输入为什么是两个MOS对,百思不得其解

增加运放转换速率(slew rate)的结构,加快运放的大信号反应速度。willy sansen的书有讲。

是不是还能够减小噪声?有人跟我说是稳定共模电压,我感觉好像也有点道理

请问那个书叫啥名字?

模拟集成电路设计精粹 清华大学出版社

WillySansen

中文版第233页,有类似的结构,是N输入的结构。

这属于AB类放大器输入端,加快运放在大信号时的摆率。

多谢,看了看果然是的

这个电路不能提高SR

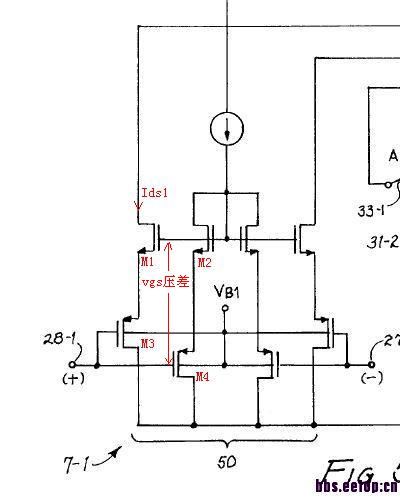

标号如下图,设差分大信号作用于输入端,左负右正,当幅度大到某值时,左半侧M1,M2,M3,M4导通,右半侧完全截止,电流源电流全部流入M2,M4,压差vgs2+vgs4达到最大值,也即vgs1+vgs3达到最大值,这时再加大差分电压,vgs压差也不会增大,所以Ids1达到饱和,如果M1,M2,M3,M4尺寸相等,Ids1=电流源电流=最大值,它和普通差分电路一样,Ids1被电流源电流限制,所以SR是不能改善的。

望形生义,本本主义,大忌也

的确不能提高摆率

继续呀……

能够让上面的NMOS管有合适的偏置,但并无提高摆率的作用

欢迎大家继续讨论

nicer

学习了!

是的,和书上那个是有差别的,那个是交叉的是一个正反馈,所以能提高速度。但是不明白为什么M4的栅接了输入,有什么好处?

Sorry,是我没想清楚,误导了小编,抱歉。

这个结构没有增加slew rate,当然交叉耦合的结构是可以的。

我个人觉得,那唯一的好处是应该是小信号速度快一些。

PMOS作为follower,产生差分电流的是NMOS。

且NMOS结构为共栅放大,没有miller效应,比共源放大要快。

总的来说,感觉这个电路的速度是快的。

当然也有缺点,offset严重,不过专利中使用了auto zero,这就不是问题了。

另外也减小了输入信号的共模范围。

如果输入信号比较接近ground,用这个结构还是不错的。

很好的电路,学习了。

M2,M4给M1,M3提供偏置

关于速度的问题

在相同的静态电流Ids1下,我们把它和普通差分作比较,标号见7楼,设差分小信号信号作用于输入端,M1,M2栅极为交流地,分析它的单侧即可,输入电压降落在M1,M3的vgs上,忽略衬底效应,

vgs1=Id/gm1

vgs3=Id/gm3

总Gm=Id/(vgs1+vgs3)=1/(1/gm1+1/gm3),它总是小于gm1和gm3,如果尺寸M1=M2=M3=M4,

Gm≈gm/2,只有普通差分一半,意味着GBW降低到一半

再看看它的ft

流过M3 cgs上的电流=Id/gm3*jωcgs,相同的电流流过M4,

总输入电流=2*Id/gm3*jωcgs ,令输入电流的模=输出电流的模,所以

ft=Id/(2*Id/gm3*2πcgs)=gm3/2πcgs/2,是普通差分一半

所以,速度不是增加,而是降低,不仅如此,因为电流源和静态电流Ids1是并联关系,所以消耗电流=2倍普通差分

另外共模范围因为2个VGS串联占用了大的电压裕度而变小了

它的特别之处在于直流特性,即具有NMOS的输出特性,而输入特性则是PMOS,当需要与第2级的高直流电平连接(在这里就是),而输入共模又要求低到0v,就可以采用它,普通差分是办不到的。

当然,也不是非他不可,也有其他解决方法,例如NMOS差分再加一级PMOS电平移位,或者PMOS折叠共源共栅,其中以折叠共源共栅为最优

這是Rail-to-rail input OPA ,主要功用是wide range operating,適用於Low voltage design!

厉害,说得很有道理