请教下LNA中的ESD的问题!

做得好的ESD大概能在200f@2.4GHz左右。如果自己做不到更好的ESD,只能用foundry的,或者干脆不用。

ESDa big topic for IC design

你用什么ESD防护器件给LNA做防护?

用的是UMC 18 中的 二极管 来做ESD 现在很难估计里边的寄生电容 ,我们现在估计是600f 有可能这么大吗?

我们用的就是foundry的ESD,流完片之后基本测不出结果 ,做电路设计时是按照200f来设计的

如果不用的ESD的话会有什么影响吗?

你可以后提提出结点上的寄生电容,仿真仿出二极管的C-V特性,二极管反偏的时候电容可以做到200fF以下,正向偏置的时候电容是反偏的2倍左右。电路仿真时带上ESD应该不会出现流完片之后测不出结果的情况。

二极管的尺寸是多少?W,L,几个finger? 2.4G窄带的LNA完全可以用二极管来防护的。

不用ESD,你怎么做产品?

如果你怀疑是ESD的寄生电容导致电路不工作,建议你做FIB把ESD器件切断再测试

不是很明白,ESD对LNA的性能有这么大的影响吗?

ESD说白了就是在LNA的输入加入一定大小的电容。对S11和噪声系数的影响都可以通过匹配来解决。

请高手指教。

另外,一般foundary提供的ESD都是给低频用的,寄生电容比较大。

我们平常LNA用的ESD,都是自己修改的较小的ESD,测试能耐2kV。

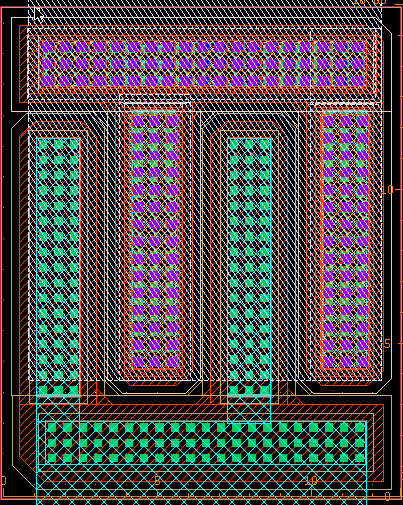

这是我们ESD中二极管的版图

现在的问题是当ESD中电容比较大的时候,对电路的影响会显著增大

低频的大概在多少范围,我们是400M,电容能有多大

寄生电容对LNA性能的影响有理论推导的,公式比较复杂。总的来说,它对输入匹配,功率增益,噪声系数,IP3,线性度都会造成影响,也许对有些性能影响不大,设计仿真时带入ESD器件你就会发现。

我看diode的layout面积也不大,3umx10um, 2个finger。我感觉没问题

你先看电路的DC点是否正确吧,是否焊接的时候已经被ESD打坏了?

接下来再做FIB把ESD切掉再测试,没有ESD,焊接一定要注意,做好静电防护措施

给你一些tsmc的信息吧,

我们用的tsmc 65NM的IO,里面有各种用途的ESD/IO

PDB1AC100fF1kV HBMLNA

PDB2AC300fF2kV HBMLVDS

PDB3AC600fF2kV HBMADC/DAC

我们也看过IO里面的ESD 电路,analog IO都是diode device

digital IO可能会有GGNMOS之类的,但是MOS的IO寄生会很大的

RF的ESD肯定要用diode了,SCR不太敢用的,不能像在foundry,有具体工艺参数,能够反复尝试

还有,个人ESD diode尽量finger多一点,有时候周长比面积更管用哦,

很多diode ESD时靠侧边导电, current不走体内的

反正200fF的寄生应该说差不多吧,PAD及走线尽量用高层metal

等到封装完了,你就会发现,最大的寄生电容居然是bonding wire 引入的ESD的几百个p算个啥阿 :-)

这个时候你不得不增加 bonding wire的尺寸.....一眼难尽

finger多一点有什么好处?寄生电容是按周长算得吗?比如一个 100*80的二极管,周长缩小10倍 ,寄生电容会同比例缩小吗?

我不是说么,在同等面积下,周长大的diode肯定比周长小的diode ESD level高,

所以在同样的ESD要求下,周长大,面积就可以小一些,自然寄生也会小一些

bipolar的电流集边效应会挺明显的,diode应该也会有类似效应,所以建议还是finger多一些的为好

还有楼上有一位说的package是一个重要的问题,他说的bonding wire电容

其实bonging wire的寄生电容应该很小的,电感到不小

但是package的引脚会有很大寄生,根据不同的package是不同的

要高速寄生小,那么就要BGA或者QFN封装

QFP会便宜一些,但是寄生不小

DIP就更差了,寄生大大地

我们走的是MPW ,可以作FIB吗?

跟zhukh探讨一下这个问题。

我知道您说的理论,我也看过。但是我以为,这些理论和数学推导都是建立在单一匹配器件(串联电感)的基础上的。

而一般做产品时,为了满足一定频率范围内的S11,匹配器件都是3个,甚至更多。因此我觉得不存在很多教科书上所说的问题。

做FIB与MPW无关,你只要选一颗芯片,然后decap,就可以做FIB了。但是估计FIB后拿回来芯片就不能焊接到板子上了,必须用socket来测试。

只是讨论下,RF电路我不是专家

也许寄生电容大一点你可以做匹配把它吸收掉来满足input matching, 但是加的元器件越多,insertion loss也越大,insertion loss是直接加到整个系统的Noise Figure上面去的,总得trade-off, 可以这样分析吗?

Thanks for ESD .

Thanks for ESD.

一般片外做匹配用的电感和电容,Q都很大,寄生电阻很小,不会损失什么功率,因此insertion loss很小。

主要还是考虑集成度的考虑,片外器件不能太多。但是为了满足一定频率范围内的S11,工业上片外匹配器件一般都不止一个的。

我只是对ESD会造成LNA性能的影响这种说法比较疑惑。

我觉得在片外器件不止一个的情况下,尽管ESD引入的寄生电容,都可以匹配到想要的位置,因此我觉得对LNA性能的影响其实很小。

欢迎大家就此讨论!

ESD 的寄生电容会增加LNA对匹配网络的敏感性,并且增加匹配网络里的噪声

差不多一年前我写过一个文档,对带有ESD和不带ESD的LNA分别进行了仿真和性能比较,仅供参考.

500fF是可能的!

nice...

请问文档哪里下载?谢谢!

点击上面的“文档”两字,我做了链接的

http://www.khesd.cn/Diode_091118_Kehan.pdf