LDO仿真出现右极点,但输出稳定,不明白原因

时间:10-02

整理:3721RD

点击:

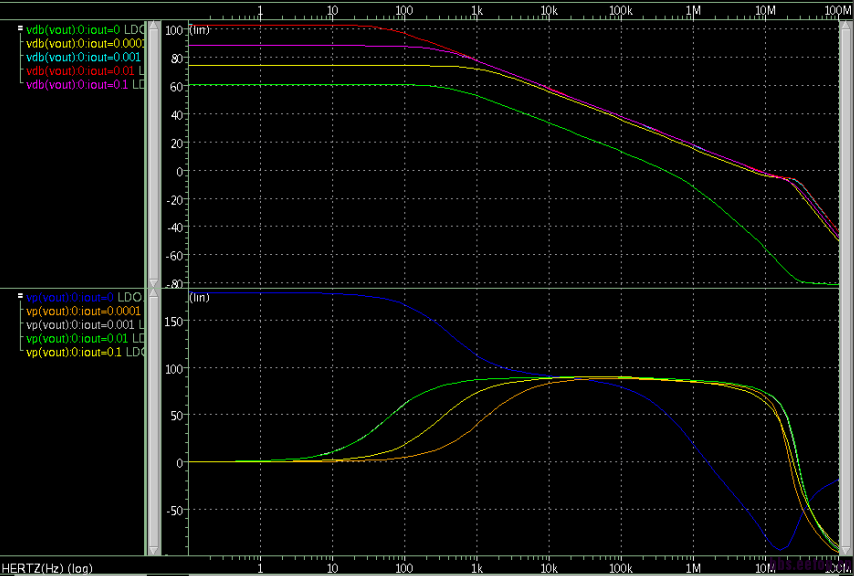

最近在仿真A 0.9-uA Quiescent Current Output-Capacitorless LDO Regulator With Adaptive Power Transistors in 65-nm CMOS这篇文章的电路时出现了一个奇怪的现象:在重负载的时候相位是从0开始上升的,一看lis文件发现主极点是右极点,我觉得是由于Vsen的这条环路(Ma1—Ma2—Ma4—M6)为正反馈所以引起了右极点。但是文章给出的波特图相位变化跟我仿真的不一样,而且我观察瞬态仿真的结果也是稳定没有振荡的,我就糊涂了,出现右极点还能稳定?不知大家有没有遇到过类似问题,求大神解答O(∩_∩)O

大神右极点怎么看出来的呀

我看仿真结果文件的,在波特图上面也看得出,正常是从180开始下降,我的是在重负载时从0开始上升

如果右半平面极点在高频,而你加入的脉冲上升速度不够(如上升时间太大,如100us),仿真的时候也是稳定的,但是只要有右半平面极点,上升时间足够小,肯定是会不稳定的。

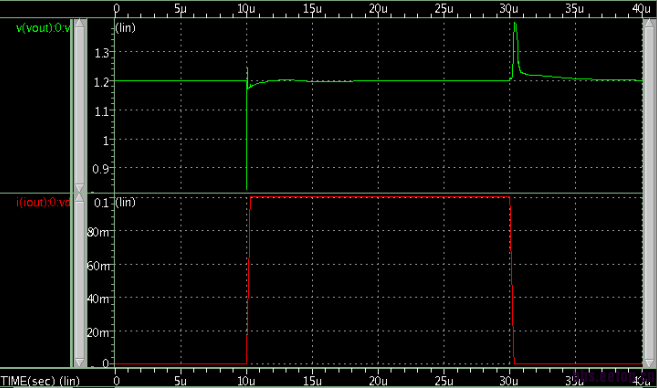

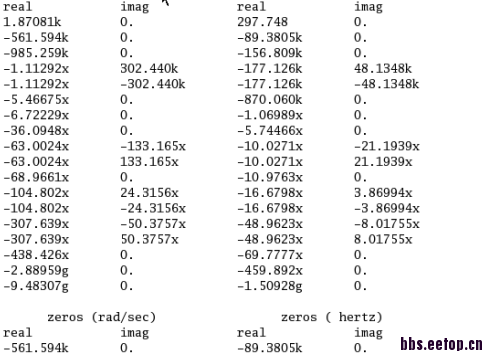

我的右极点是主极点,只有几十到几百HZ,我加的脉冲上升时间300ns,也是稳定的,看看我的仿真结果就知道了。

顶起,我也遇到这样的问题了。

相位裕度是多少?貌似你的都够。有右平面极点也不一定就震荡。你看看有没有其他零点或极点可以抵消?

过冲太大,补偿过了?

过冲大貌似没办法,输出电容100p,而且时间那么短零点零几us应该没事

相位裕度足够,不知你说的抵消是指什么,用零点来抵消右极点?

对,零极相消!同一个半平面的零点和极点可以完全抵消。右极点是幅频:-20dB/十倍频程,相频:45度/十倍频程。有右极点,不代表必须震荡!而且你的相位裕度也够。

谢谢,受教了~