做FIB用的顶层金属方块边长和开窗一般是多大啊?

请问一般的金属大小和开窗是多大,在国内做FIB的时候能用探针直接扎上看信号啊?谢谢!

这个“开窗”指的是在钝化层上开窗露出顶层金属的意思吗?

如果是的话,那么foundry给的rule都是有明确定义的,比如PAD的开窗,CSMC0.5工艺用在PAD opening上的开口定义为CP,最小是90μm*90μm,但是当金属做熔丝需要开窗时可以不按照这个最小尺寸来,可以做的更小(DRC可能过不了,但是忽略这个问题),同样,做测试用的顶层金属开窗也可以不用做到90*90,你问需要开多大,以及有么有厂商可以做这样的测试,答案是当然可以的,在中测的时候,片子还在整个wafer上,没有划片,直接用探针扎上去,需要开多大口的问题你需要联系帮你做测试的厂商问问他们,但是一般超过10*10就应该是可以的。

多谢!开窗指的就是这个意思

CP时候的probe PAD固然大,边长几十um,无论是做poly fuse的PAD,还是仅仅发送数字信号的PAD都一样。

我说的是封装后,到lab开盖做FIB,直接用探针去扎这个点,用示波器看信号debug

这个你有点想当然了吧,你确定可以封装完了回来“开盖”做测试?这个方法我不清楚啊,我知道的是直接在wafer做测试,论坛里有很多大牛,见识广啊,等着他们来回答吧······

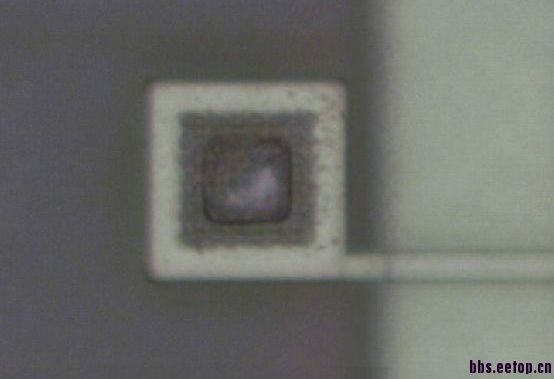

我试过在展芯试过这样测DC电压,开盖后,可以挖开钝化层,生成20X20u左右大小的PAD,这个PAD连接到需要测试的那条metal上。然后拿到探针台上给芯片上电,再probe那个PAD。不过生成这个PAD的过程很慢,一个小时生成一个,而且收费比上普通探针台操作贵,一个PAD也就用探针扎个两三次就氧化掉了。

这个经历确实有意思,应该是在超净间里面做的测试吧,而且这个实验应该是测的别人的芯片?如果是自己的芯片完全可以事先预留测试窗口,不用一个个挖啊。另外,这种方法也只能测芯片边缘的预留PAD,实际上,一个芯片初次流片时应该是可以在整个芯片的任何位置(而不是只能在边缘)预留一个稍微大一点面积的顶层金属,并在这个位置上定义一个pad opening,这样的测试更灵活。

忘了是不是超净间了,进那实验室的时候鞋要用塑料袋包起来,PAD是另外一个实验室里面生成的。

是自己做的芯片,不过整个芯片都没预留探针点,少数的芯片出了问题只能用这个方法,弄了很多天

就是请教这个顶层金属和开窗的一般大小

对于淀积pad大小你一般不用关心啊,因为这个都是按照个来收费的,你想淀积多大基本都可以。一般fib淀积线比较费时间,是按照操作时间收费的。线宽在北京基本是1μm吧,其他地方服务不知道。

开窗--- 都是操作人员关心的事,其实你不必太操心。

开盖点的探针有软针和硬针,软针有1u的,硬针一般最小10u,你的开窗够大了啦,

看探针大小

谢谢大家!就是问这个FIB探针的大小