增加3dB 带宽

设计要求

1.设计一个单输入单输出的运放,结构自定,带宽0-10MHz,带内增益50dB;

2.输入阻抗>20kΩ,输出阻抗<50Ω;

3.带2pF电容,实现-3dB带宽下15MHz。

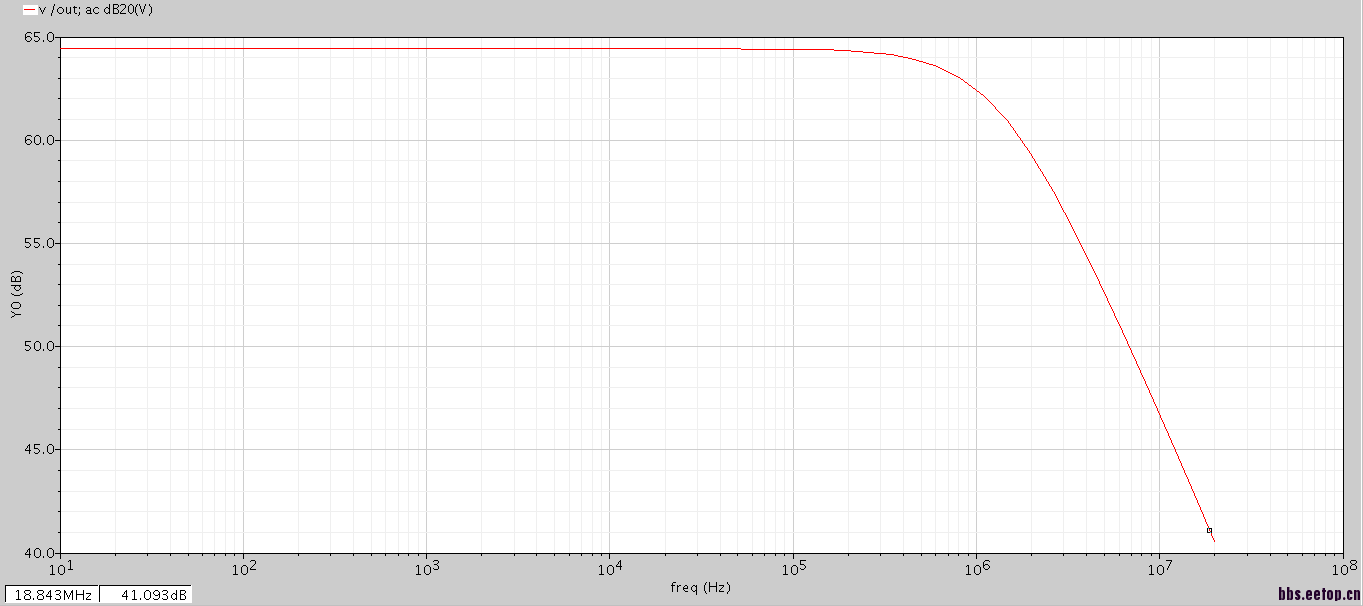

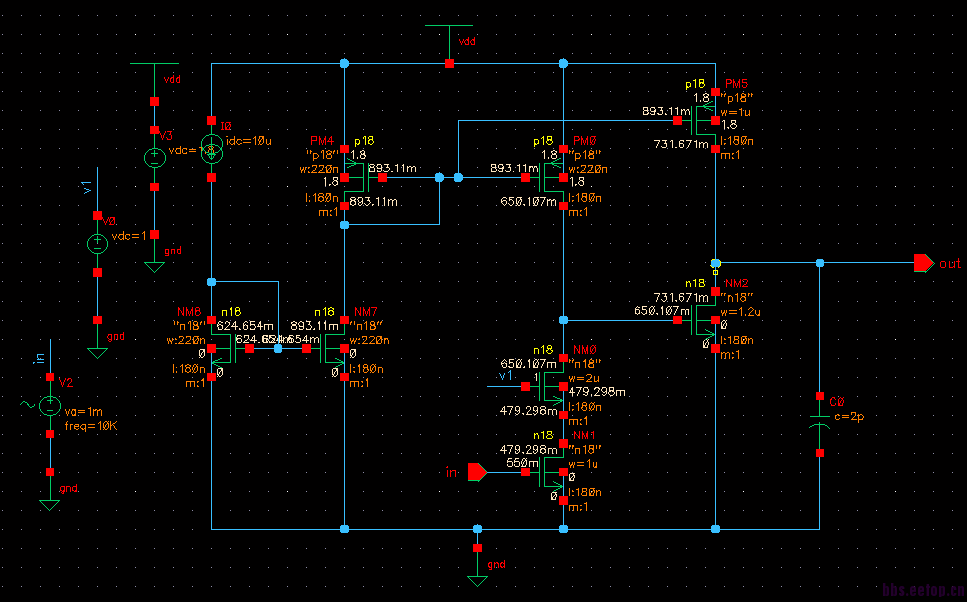

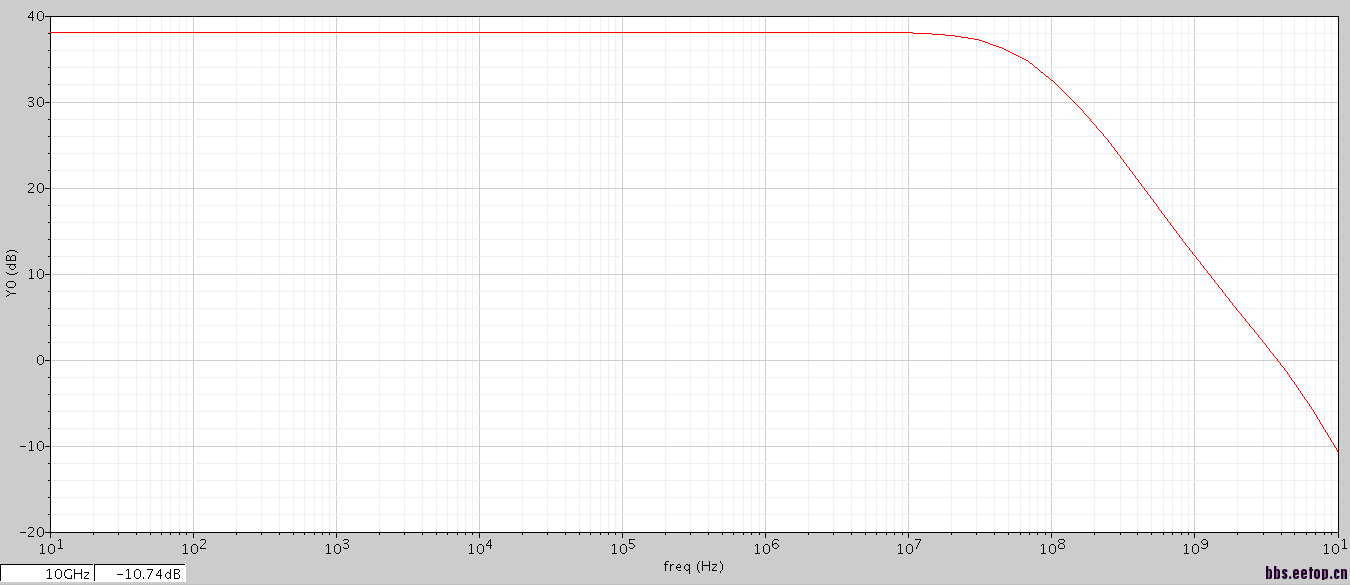

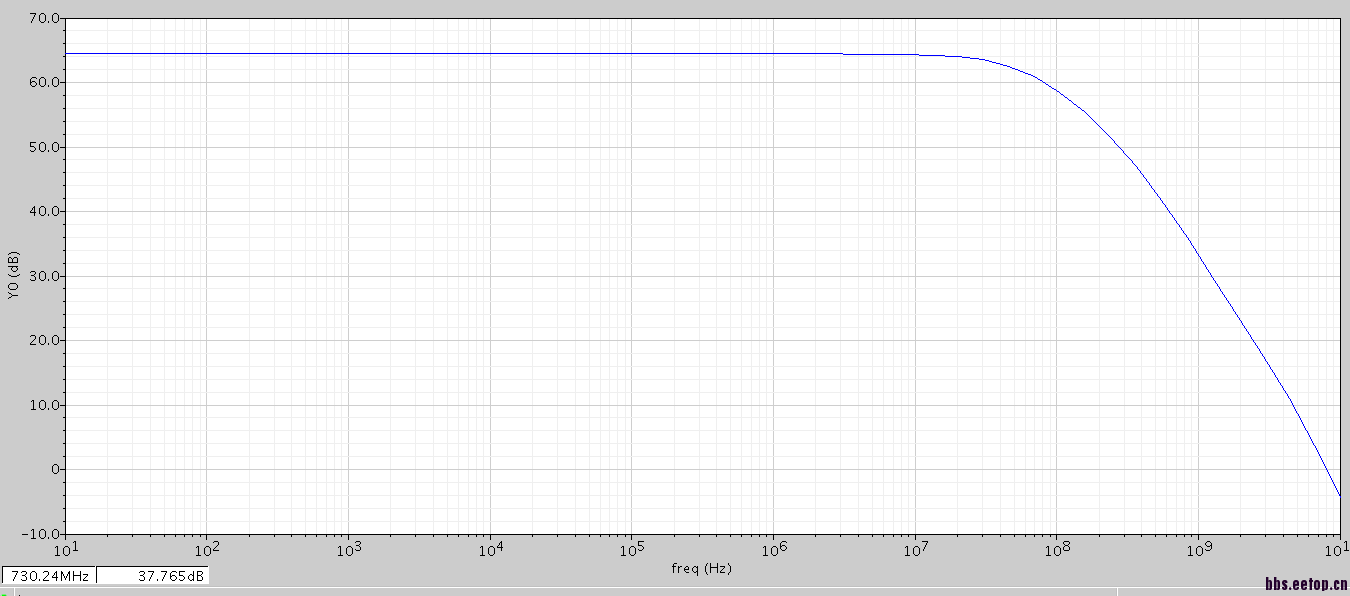

设计的放大器中频增益是64.4dB,中频带宽也达到了400+MHz,但是带上负载电容之后3dB带宽竟然只有1.3M,求大神指点迷津

如果主极点在输出端的话,那么其频率P1=1/(2*Pi*Ro*CL),你的P1=1.3MHz,CL=2pF,可以计算出Ro=61.2KΩ,跟你的设计要求Ro<50Ω不符。如果Ro<50Ω,CL=2pF,很容易计算输出极点频率Po>1.59GHz,这应该不会是主极点。要使输出电阻小的话应该用缓冲结构吧

接着往上顶

真搞不懂为什么总是有些人不假思索的在强调-3dB带宽

有一种东西叫增益带宽积,或者叫单位增益带宽,-3dB带宽与其开环增益直接相关

-3dB 15MHz, gain 50dB, 那么opamp带宽大概要5GHz

还有一点,区分opamp和amplifier,一个是闭环应用,另一个可以开环应用,稳定性要求是不同的

后面加上一级Source Follow就满足要求了

源跟随可以将输出电阻降下来,但是不能降低到50欧以下吧?而且更麻烦的是3db带宽不够,很烦

想要用电压串联反馈的方式降低放大倍数以增加带宽,同时降低输出电阻。中频区的增益带宽积好像满足指标,但是按照你的计算方法(其实我是一个新手,不知道主极点什么的),不知道这种想法可否将输出电阻降低到50欧时,带宽也满足要求,求继续指导。

xuexi zhong!

菜鸟表示谢谢指导!但是还是不知道,接下来该怎么修改。求继续指导>>>>>>>>>

4楼所述正确,如果要求15M处还有50dB增益,那么带宽增益积太大了,这个要求你没有搞错么?

真心看不懂这个

1.设计一个单输入单输出的运放,结构自定,带宽0-10MHz,带内增益50dB;

2.输入阻抗>20kΩ,输出阻抗<50Ω;

3.带2pF电容,实现-3dB带宽下15MHz。

首先 这种单端输入的运放怎么使用。

其次,第一个条件的“带宽0-10MHz”是什么意思。

再次,50dB大约是1000/8倍,GBW = A*GB 大约是1.5G。

最后,还是不觉得这个东东呦啥意义

嗯,是这样的。10MHz以内gain=50db,-3db出现在15MHz处,也就是说15MHz大概为47db。

这个仅仅作为老师布置的作业,我不知道如何下手,所以才发帖求助。至于放大器的实用性目前不是考虑的范围!