Post-layout simulation龟速,如何破

时间:10-02

整理:3721RD

点击:

芯片画好了需要做后仿,用spectre一天都跑不完,而且经常跑着跑着就崩溃

请问大家有什么好的方法做模拟?

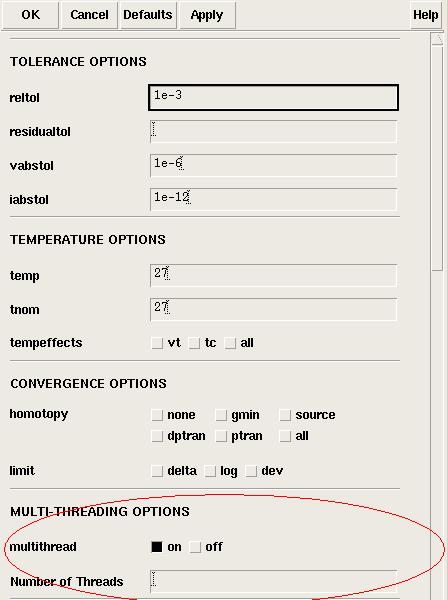

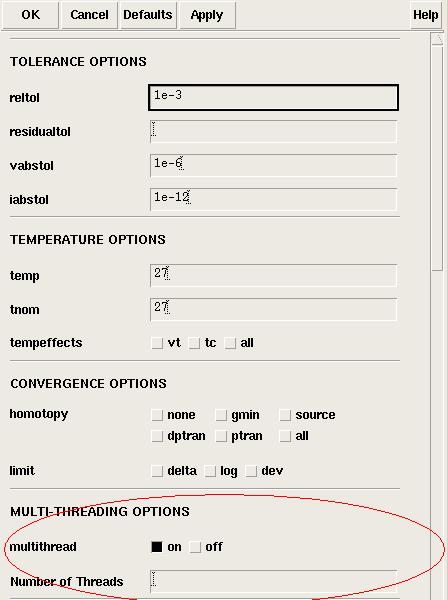

如在simulation->analog里调整收敛和homotopy

如果在output-saveall 里面做文章

求助!

请问大家有什么好的方法做模拟?

如在simulation->analog里调整收敛和homotopy

如果在output-saveall 里面做文章

求助!

正常,慢慢等

由于netlist大了n多倍,存所需的节点,否则tran基本会爆掉

看看有没有aps或multithread

换用hspice可能会好点

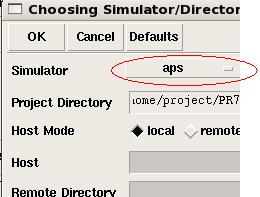

不是混合信号就用aps

混合信号可以用xa+vcs

aps和multithread是什么...

请问你说的那两个是仿真器还是软件?

前者是加速跑仿真的环境,后者是用多CPU核跑仿真的设置。

仿真器

我cadence上好像没有这东西....

装了。好像设置有点儿问题不能run

*Error* Simulator Executable 'aps' cannot be located from $PATH

Use setShellEnvVar() call to correct your path in CIW

你知道怎么破么?

俺只知道怎么用,不晓得怎么装啊。

xuexi zhong!