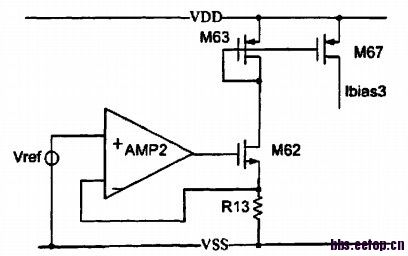

关于基准电流源的一个问题

这个图是没问题的,通过负反馈运放将两输入端箝位在相同的电压这也是没问题的,你需要好好观察一下直流工作点以及环路极性

学习学习

放大器的增益不够高的话,就会出现你说的放大器两个输入端电压不等的情况。先把放大器设计好。

电阻本身也有温度系数

3楼应该说得对,应该先分析一下静态工作点。对于放大器的共模、差模输入范围等先分析一下。然后在选取合适的输入参数重新仿真。也注意电源电压的选取。

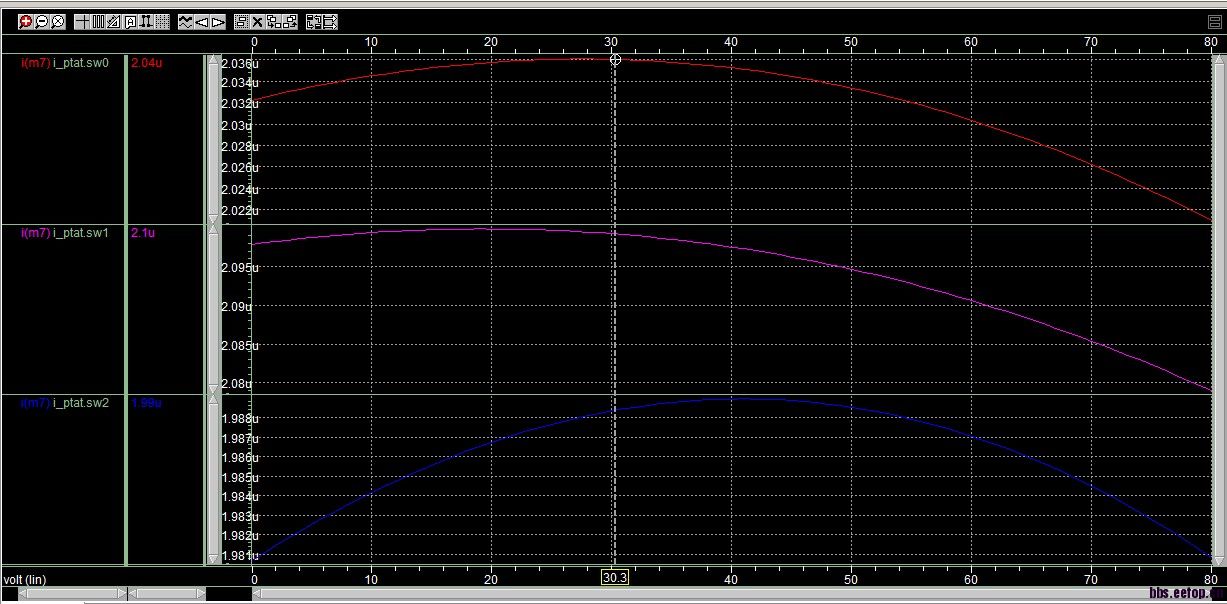

我把运放的增益设计成75dB,运放两个输入端电压也没有完全相等,我在做DC扫描输入电压的时候,有一段是相同的(大概是0-0.6V),有一段就偏离了(0.7-1.8V)。

你的电源是1.8伏?那你的放大器的共模输入范围很小。如果你的输入对管是PMOS,就会有你仿出来的情况。你可以调整一下P输入对管所用的P电流源的饱和深度,调小一点换回来共模输入范围大一些。

电源电压多大?输入太大的时候管子进入线性区了,运放的增益就减小了。这种结构调整基准电流一般是通过调节电阻大小实现的,不会让基准电压变化太大

估计是环路稳定性问题。

负反馈原理

可以把电路图贴出来,一看便知

电阻的温度系数会影响电流不用考虑吗?

我也仿过这电路,得到的结果是I13不等于V13/R13,不知道为什么。

估计还是你运放的输入共模问题,1.2V输入不能保证输入管工作在饱和区

可能运放的Vos电压太大

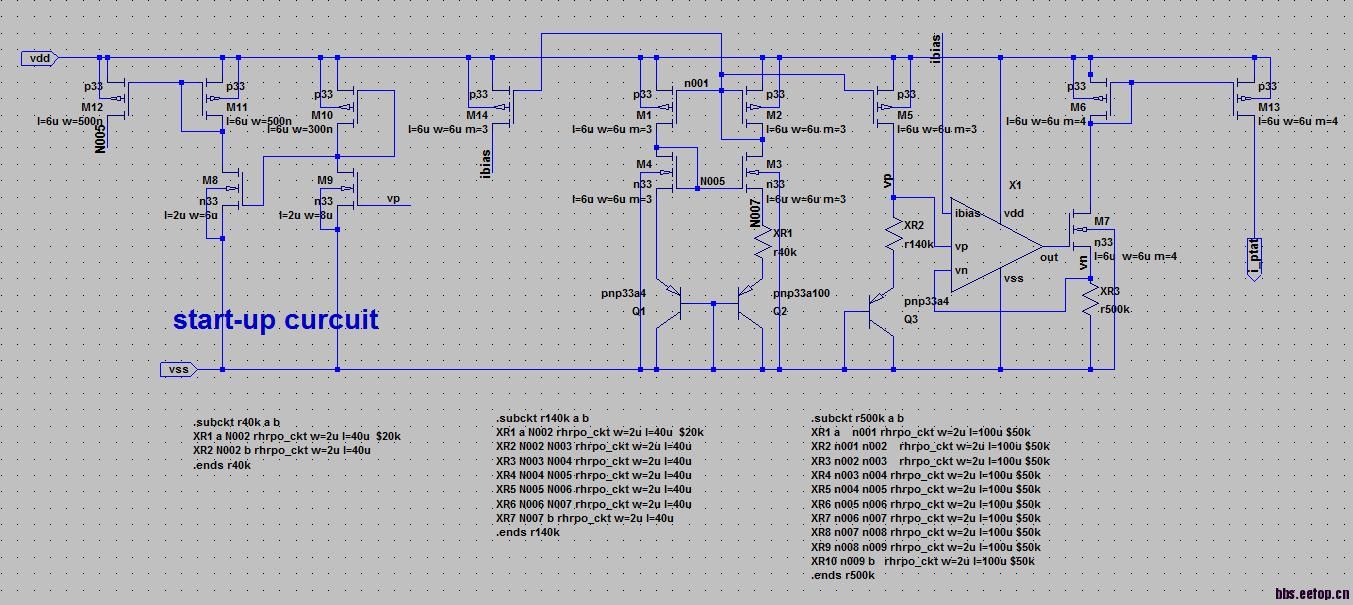

建议小编把详图贴出来,就一个原理图是看不出问题的。我以前做过这种结构,贴出我的电路图希望和大家探讨探讨,最好提出我的不足之处。其中运放是P管输入,miller补偿二级差分运放。

注意运放的共模输入范围和最低工作电源电压

这个基准电流,电阻工艺偏差怎么办?

luguo

没有校准的话,有多少算多少。

嗦嘎学习了

同意四楼意见 同时注意电压VDD取值

这不是很常见的电路吗?我开始学IC的时候就见过了。

注意M62管的GATE电压,此处也是运放的输出电压

this op-amp in this circuit makes the two input same. so, the voltage across R13 is Vref. the current of M63 is Vref/R13. so the output current of M67 is Vre/R13