请教---1.8V NMOS Vgs耐压多大?

时间:10-02

整理:3721RD

点击:

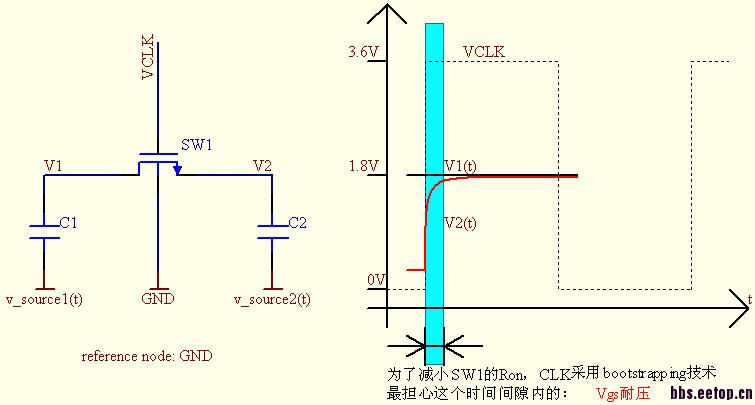

0.18工艺的1.8V NMOS,Vgs加一个脉冲宽度为12ns, 幅度为3.6V的方波时钟信号时,会使该NMOS击穿而损坏吗?如果把幅度减到2.8V呢?

实际大概的电压响应过程如图所示,其中,v_source1、v_source2详细细节未展开,目的是保证如图所示的电压响应曲线。

1. 最担心的是:如图中所示的时间间隙内开关SW1 Vgs的耐压;

2. 该电路目标是用于论文中的实验性电路。

谢谢各位提供宝贵的意见!

都不行

不同的工艺是不一样的,你可以咨询代工厂;

与栅氧化层厚度有关,spectre会按1nm耐压1V来计算,但最终保证耐压程度的还是foundry 的测试文件,在PDK中你可以找到相关的文档。

3.6V寿命会很低,2.8V寿命也会下降。

做产品的话,就不能了。

看来你是过来人。谢谢,大哥!

不少人持有这样的观点,所谓寿命和工作电压(栅压)反比关系。你必须列出理论根据,说明机制原理,或者列出实测的实验报告,否则视为主观臆想。

这是反驳么? 1.8V的deviceVgs上3.6V/2.8V肯定不行,要不foundry为什么要规定+10%的power呢?

虽然foundry 会留一定margin,但不至于留这么多,而且应该由reliability的report,自己可以去查一下就知道

就这种case有点像esd test时出现的over stress,3.6V差不多是极限了

实际大概的电压响应过程如图所示,其中,v_source1、v_source2详细细节未展开,目的是保证如图所示的电压响应曲线。

1. 最担心的是:如图中所示的时间间隙内开关SW1 Vgs的耐压;

2. 该电路目标是用于论文中的实验性电路。

谢谢各位提供宝贵的意见!

不错 讨论

几个ns应该可以 关键是在产品使用寿命周期内 不能多次出现

所以还是在可靠性上会出问题

查了下某FOUNDRY-。18仿真模型的VBOX参数,达到了POWER电压的200%?

你使用 boot strap 是否因為 V2 charge 後電位變高,sw1因為 VG=1.8v

跟本無法 fully turn_on ?