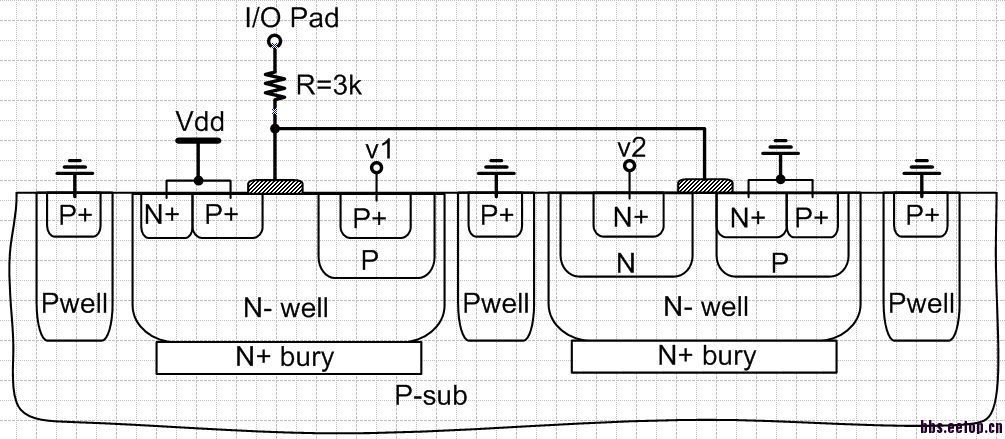

这个结构是否会发生Latch-Up?

时间:10-02

整理:3721RD

点击:

当I/O信号有较大扰动(扰动>Vdd)的时候,下面的结构会latch-up吗?

我觉得IO信号会通过栅极交叠电容耦合到P+区和N+区使BJT导通,有可能吗?求大侠指点,不胜感激

如果可能的话用双层Guard-ring可以改善吗?

补充:N- well的浓度很低

这两个MOS管是高压管。所以看上去和普通的不一样

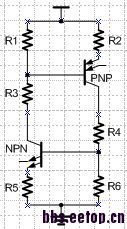

Latch-up的发生一般是NMOS或是PMOS的输出端变化,此时输出端对衬底电容有充放电动作,导致寄生三极管开启。你的电路的右边的高压NMOS的衬底电压和P-sub之间有NMOS的Drain端隔离。所以发生Latch的可能性基本没有。

非常感谢您,我再看看其他地方有没有LU,debug真头疼

您好,我想再请教您一下,高压MOS的结构是工艺文件中要求的结构,NMOS源区的N+区和P区的边缘是重合的,(这地方我怀疑NMOS的源和漏始终会通过N-well相连,虽然N-well的浓度非常低。但人家工艺厂家既然提供这种结构说明NMOS结构是没问题的),那我下面蓝色部分的latch-up电路会形成吗?再次感谢您

我是不是发错版块了?求小编把我这帖子移到latch-up版块

感觉你的图中ring都打得很好,不会产生你所描述的latch up现象。现在你能够确定是这里有问题么?做了EMI的测试么?

你红色标记部分的N+和Nwell是不可能相连的,否则整个高压NMOS的源极和漏极就短接了。N+和NWell之间会有P-body,用来反型产生沟道。

再次感谢!我在看看别的地方

我现在也只是猜测。偶尔情况时,探针与IO接触就会产生LU,不过vdd-gnd的电流人为限制了,没有烧毁,具体看那部分失效还要到其他地方做测试,我也是第一次搞,现在只是在layout中查找哪些地方会出现问题

膜拜一下

觉得有可能 可能性还比较大