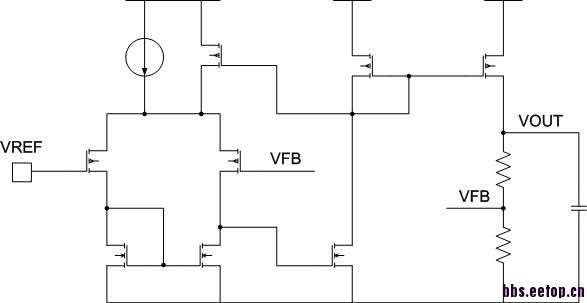

有谁见过这样的LDO结构吗?

哪位大牛能帮我分析一下这个LDO结构,这是一个实际量产过的电路,关键是没有特殊的补偿

希望帮忙分析

谢谢了

另外,哪位朋友有类似结构的paper,能否分享一下

谢谢了!

这个LDO的负载范围从0~50mA,电源从2.7V~3.6V,外部电容是普通的1uf的陶瓷电容

自己顶一个,期待解答

load current 变大时,输出的阻抗就小,dominant pole就变大,first non-dominant pole 在第一级的输出,这时,第一级current source 变大,第一级输出阻抗也就变小,所以有一定的补偿。 我印象中qcom的一篇jssc貌似就有这类似的思路,印象不深不确定。

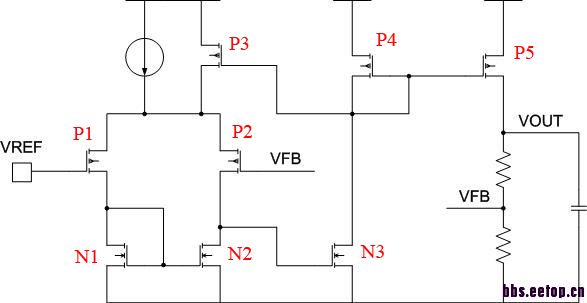

没见过这种LDO,试分析一下。输出极点是主极点,由于P4的二极管连接,N3的miler效应显著降低了,所以N3栅极的次极点往远离原点的方向移动。P5栅极的次极点也远离原点了。由于输出极点是主极点,ESR电阻的大小对稳定性影响比较大。

感谢各位的回答,我尝试计算了一下,感觉好像次主极点在N2-N3这里,因为P4的gm很大,所以这里的极点频率较高,感觉变成了第三极点

不知道是怎么回事

继续顶起,哪位朋友有类似结构的论文,能否分享一下

谢谢了

继续顶起,哪位朋友有类似结构的论文,能否分享一下

谢谢了

这个结构我在nrf24l01里面见过类似的,但是有些差别,差别在于那个ldo在运放的输出端有较大的R与C串联到地。你画的这个结构LDO感觉好难稳定。

可它确实就稳定了,没有其他的额外补偿,经过量产验证了

用了什么规格的电容在什么load 电流下稳定 ldo本身耗电流多少

同问,该LDO的输出电容,负载电流范围,静态电流,和全载时候的电流。输入输出电压。

要具体分析要因,要保证原理上正确,有理论依据

不要老是量产了怎么怎么样,量产并不是万能的,这次不出bug不代表下次不出bug

因为比较marginal的电路会再应用条件改变的情况下出现问题

我还见过电路都振荡了但是能有function的量产chip呢,而且是每个月kk量级的

LDO 的稳定性跟负载有很大关系,如果你的负载是已知而且固定的,这就比较容易

如果是人家那种单颗LDO芯片,由于应用范围很宽,有轻载有重载,电容也有大有小,

所以LDO的稳定性要考虑很宽的范围

总之具体问题具体分析

这个LDO在dropout时有很大的漏电,这个缺点很致命的。

其实和一般的两级的传递函数基本一致,所以稳定性是没有问题的。它的最后一级是驱动输出级,和前一级是成比例的,电流镜像比例很大(几十比一)。在模数混合系统中,它主要优点是最后一级可以随时关掉,以降低静态功耗,并保证反馈环路稳定。

P4和N3看起来像是运放的输出缓冲级,这一级的增益很小,类似于源极跟随的左右用来降低运放输出级的输出阻抗,而为啥不用直接接个源极跟随结构,可能是为了考虑调整管P5在工作范围内的直流工作点设置有关系,另外也起到了极点跟随负载自动调节运放尾电流的作用。主极点在输出端,次极点在运放第一级,它们的比例可能是固定不变的,也就是不会随着负载的变化而变化。主次极点只要两者在空载时的比例选取得当,LDO的环路是可以稳定的。

感觉这个分析比较好

感谢各位的分析!

这是所谓动态偏置的LDO,最大的限制有两点,一是偏置电流切换会影响输出ripple,二是输出负载范围没法做到很宽。

主极点确实是在输出端(因为大电容的存在)……负载大电容会有一个寄生的esr电阻,这个电阻是和大电容串联在一起的,在输出端形成了一个零点,这个零点是为了补偿次极点,因为主次极点相隔太近的话,会恶化相位,所以采用零点补偿,将次极点对象为的恶化补偿掉……

我总感觉,从N2-N3-P4-P3构成了一个正反馈环路

N3's gate cap is not that large -> pole of 1st stage can be separated from the one at the output stage.

同意,N3-P4应该就是个平移电位用的,没什么增益,主极点不在这。可以理解为单极运放作EA。单极运放很容易稳定。

我想應該是嘗試讓內外兩個pole維持特定的關係,不要因為

外面pole的因負載變化的改變讓兩個pole太接近,此外也可

以加快Error Amp的速度

是正反馈。不过,只要保证环路增益小于1就OK了。动态调节尾电流的电路基本都有类似的正反馈。