求助,流片后基准分压失败!

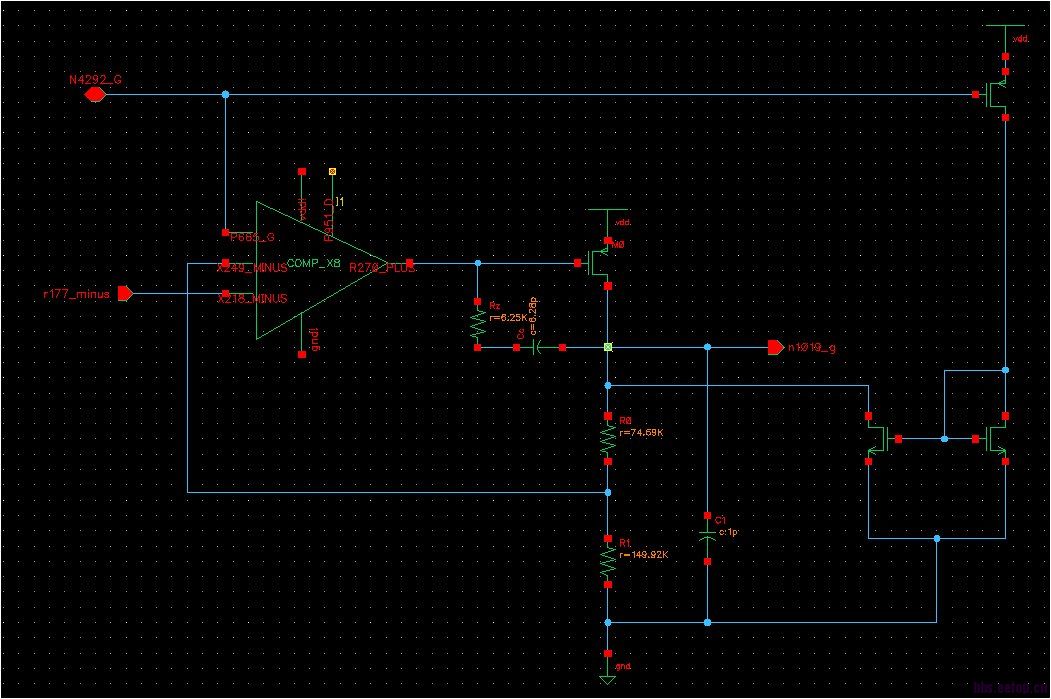

图中N4292_G是基准电流模块镜像出来的,提供偏置电压,R177_minus是基准输出,为2v,经过带负反馈放大器后输出n1019_g为3v。现在的问题是:2v基准出来了没问题,但是输出不为3v,为4.7v左右。

这个模块前仿后仿都没问题,作了corner也没问题,不知道是什么原因,求指导

放大器出来后的pmos管W/L=20/1,M=4;电流镜左边管子W/L=12/2,M=8;右边管子W/L=15/5,M=1;右上方管子W/L=3/5,M=2;N4292_G为3.43v,电源电压5v,放大器开环放大倍数800多倍

这个只能多测几个点,找原因了

电源电压时多少

电源电压5v

开始是怀疑工作在临界条件,但是仿真开环低频增益为46db,相位裕度90;闭环的时候主极点非常大,几乎是等于带宽,估计电容补过了,但是应该就是非常稳定才对

5v电压足以使偏离临界很远( 管子尺寸正常的话),可能是有的管子尺寸不正常,导致有些现象没仿真到。

还有感觉你的电路结构收敛比较困难,所以仿真正确,实测有误,就觉得是比较正常的事了。

就算震荡,测得的中心值也应该是3V啊。上次有个人就问过类似问题,结果是运放偏置的原因

能详细说明下吗?我刚开始做电路,一点经验都没有

流片后一共是测试的四片,输出值分别为3.8004.710 4.740 0.117 。由于当时是别人测的,也不知道测得振荡没有,返回的报告结果是这样

有没可能是esd挂了,不开电测试一下输出对地电阻对吗,若不是,建议用示波器看输出波形

ding

keneng可能偏置就没有给对

先看看静态电流是否正常吧!

运放增益小了点。如果应为工艺偏差在开环增益再减个几DB,输出也不准。不过最可能的原因,你运放的2个反馈电阻匹有没有问题。

这种结构有问题的电路,仿真有可能是对的,但是制造出来有问题一点都不奇怪。

多数电压都不同,我觉得不是振荡的原因,就算振荡了,一般也就是比较小的纹波,不会像环形振荡器那样的

2 item:

1) opamp 输入pin, 是否为负反馈(应该不会..这种错误也太低级了)

2) checkM0 工作状态。, 是否有如果的电流维持电阻电流+镜相电流 ..

可以做fib, cut断镜相电流try一把..比较疑惑..why add the currentloading.?

难道用做power regulator ?

那就挂一resistor loading匹配, m0工作点。.

输出端挂大电容.try一把, 1nf左右。.

测出来的数据有点矛盾。

有4.7V又有0V的。不太可能。

估计测错了。

电阻匹配应该没问题,用的是同一阻值同一类型的电阻,通过串并联而来,我是把怕大家看不清楚将它简化成这个样子的

现在的判断看来确实不是振荡的问题,过几天再测几片

1。输入是负反馈,这个没问题的

2、加电流镜我自己是这样理解的:一是M0管的电流加大,电路和速度提高了,因为整个电路的相位裕度很大,速度很慢,因此提高速度有必要;二是M0电流加大后M0的棚电压降低,这有利于提高放大器的精度。

其实我将电流镜去掉后仿过,从仿真结果上看没有问题

可以把更详细一点吗?

如运放以及外部的尺寸,如果方便的话,把从带隙基准出来的偏执也给出来吧。

已经给了,麻烦分析下

我如果帮你解决这个问题,我们能谈谈待遇的问题吗?

楼上的,你解决了,我叫小编给你五个信元哈

首先解释下,你的current load是什么回事。如果要得到3v,下方loop就可以,current 那边是干什么的

你说的彭电压是过驱动电压吧。唯一的情况就是你的M0 pmos进入了非线性去,或者饱和取,你测下,此时pmos的gate电压时多少。再有就是你的opa是否工作,也是非常重要的。