请教关于折叠共源共栅的仿真问题。

这点令我很困惑,之前仿真其他结构的运放时,用lis文件里的参数推导出来的值基本就和仿真结果是一致的。为什么折叠运放差的这么厉害,大家能给予一些指点吗?

加不加gmb这一项,就要看你的电路中存不存在衬底偏置效应了,如果存在,当然加上gmb肯定得出的结果更准确。如果不存在,就没有必要加,即使加了由于Vbs=0也不起作用。折叠运放中,本身在推导输出阻抗中就用到了大量近似,其实在不同静态偏置条件下应该是有不同的近似的,但是在推导这些输出阻抗时都是一概而论的,所以实际仿真出来的结果会有较大的偏差。我是这样理解的,不知道你觉得如何?

增益不仅跟gm有关,还有Rout,Rout的结果很难算准的,所以仿真与计算的相差6dB很正常

恩,我懂你说的意思。我是手算把后管子工作点都搞好后,因为有偏差所以就在hspice仿真文件.lis里用那些仿出来的gm,gmb,gds再按公式推导,结果是差了两三倍。

具体问题在哪,我也不知道。

2# lzd

我想这个问题是在于仿真模型,你利用list文件中的具体数值,代入了常规公式,这些常规的公式多半是建立在长沟道器件的基础之上,有太多的效应(譬如沟道长度调制效应,迁移率变化,速度饱和,短沟道效应等影响的阈值电压变化)被忽略。因而,基本的电流和和栅源电压、漏源电压的函数关系需要被修正,可是你并没有修正(指你手工计算时),因而产生的影响是跨导的变化,这个变化可能是非常复杂的。但是我相信你用的Hspice仿真模型比你手工计算的模型要精确,所以导致的结果的偏差就很自然了。你觉得呢?

学习了

gaorena,lihai

又想了想,你那个结果差别也太大了,都达到了两三倍。可能不仅是仿真模型的问题,我又猜想是不是由于寄生电容在作怪,但是在AC仿真中是从非常低的频率开始的,如果是那样,应该至少在低频段相近。可是按你的说法,好像不是这么回事,所以我排除了寄生电容的问题。所以回过头来,感觉还是你的在用拉扎为书中的近似公式中出了问题。麻烦你在仔细检查:一,电路和书中的一致性;二,计算有没有出错。如果这样都还是不行,我也真想不到问题的所在了。

对了,你还应该检查一下你电路中的每个晶体管是不是都偏置在饱和区了呢?这个非常重要,因为书中的公式都是假定每个晶体管都偏置在饱和区的条件下推导出来的。如果你没有确保你的晶体管都偏置在饱和区,那么出来的结果相差两三倍,那是必然的,可以让人接受。

呵呵,我觉得两三倍的偏差已经不是很大了,6dB和9dB,手算是基于一阶模型的,和仿真结果会有偏差,最大的偏差应该就是vdsat了,由于阈值变化和速度饱和,手算的和仿真给出的值有时会相差很大,比如你手算可能带的是200mV,lis里面的可能到只有150mV,还有就是不知道你的K值是怎么得到的,lis里面会直接给出gm和gmb,同时也会给出其他的比如id vth vdsat等,你可以拿这些详细推一下他的gm是怎么得出来的,就能推出具体的偏差是哪项造成的了。

我也很晕了。

架构和书上是一样的。

所有的管子都在饱和区

因为增益计算只涉及到(gm,gmb,rds)这三个参数,所以这些参数全是在仿真后的lis文件里调用,我只是想验证下共源共栅的增益计算方法。

因这三个参数都是lis文件里的,都是level 49 model。不会涉及到手算误差类的问题。是仿真出来的参数。 9# lzd

只用gm,gmb,gds这三个参数。不会是这些原因吧。 10# ludashen

话说,大家折叠共源共栅的增益都怎么个算法?

你手算也用了bsim4 level49 model? 佩服得五体投地啊

13# chenchenbeyond

sorry我对你的帖子理解有误,你的意思是在lis给出的gm和gds的基础上去算增益,是吗?然后觉得这个结果与仿真看见的波形结果有出入,对吗?

那你是用什么公式算的?可以写一下吗?就写在这里。

我想请教你算增益的目的是什么呢?

你运放应用在哪里?

m 16# ludashen

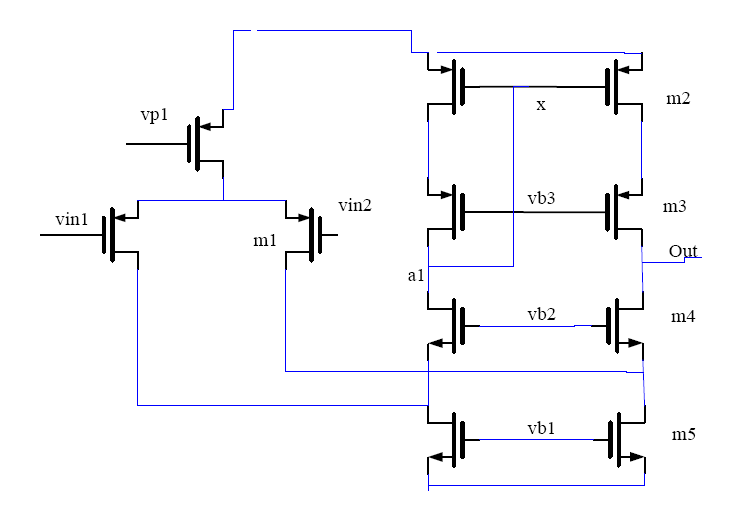

单边的从上至下依次是p5,p7,n3,n5.输入管为p1.

gm1{(gm3+gmb3)rds3(rds5||rds1)||(gm7+gmb7)rds7rds5}

这不是手算,我只是想用lis里的参数来验证这个公式。

我确定所有的管子都是饱和的

谢谢!有什么不对的地方,麻烦指正!

恩,我是新手,看书的时候对着公司以前的电路仿下。

因为其他结构的运放,手算完建立好工作点的电路。lis里的参数和小信号增益的理论公式都是对的上的。这个对不上所以我很纳闷。虽然只差了两三倍。我觉得是不是我对电路理解有问题。在公司里,电路贴不出来。

是bandgap里的,我知道你的意思是增益够了就行了。我只是想把参数和理论公式对的上。

14# fuyibin

不好意思啊,是我表达有问题。

手算肯定没这些东西,手算就是些平方率公式而已。

这个是lis里的参数套在理论公式上结果不吻合。

两三倍的偏差已经不是很大

是全差分的吗?还是双转单了?

输入是双端,我在其中一端加的ac 1

输出是单端。

全差分怎么仿真?能告诉我吗?

那就是双转单的,全差分的仿真方法你在这论坛里搜一下就有不少好资料,

如果是双转单的,公式对着呢,我也专门找了一个库里的折叠共源共栅验证了一下,没发现你说的现象,按lis中取的参数算公式和仿真的结果都在1500倍增益左右,误差不超过10%,你那可能还是有点问题,你看看你取的gm和gds的参数是不是正确的,估计是某个简单的地方搞错了,再检查检查。

实在不行可以把电路画出来,再把你的仿真结果抓图贴上,再把lis中的op参数抓出来,大家一起算算,我现在很好奇了,呵呵。

公司里电路贴不出来,我下班回家后看看抓一下贴出来给你看看。应该是我理解的有问题。一定要把这个东西给弄明白。谢谢你啊。

客气,一起研究,一起进步。

如果我记得没有错的话,

有paper指出,gds的仿真值都不太准,和实际会偏差不少。

你的学究精神要赞赏一下。

不过我觉得你有点小小的跑题了,对于你设计的bandgap而言,呵呵。

电脑是内网。用visio画了张。

vp1,vb1,vb2,vb3,vin1,vin2的dc点全是在tran下仿真提出来的。

仿AC时,我将这些dc点加入。然后再vin1 处再加一个ac 1

这种仿真有没有问题?

我试过将x点从a1处断开,在x点处加入相同的电压,但是这样的话增益急剧下降,管子都是饱和的,为什么呢?

能告诉我,我的思路错在哪个地方?

Av=gm1{[(gm4+gmb4)rds4(rds5||rds1)]||(gm3+gmb3)rds3rds2}

我只是觉得搞不懂就是对电路理解有问题。就是想搞懂而已。呵呵

你求直流工作点为什么不用DC呢,而用tran呢?其实不需用扫就可以直接得到静态工作点。你的电路中为什么vb3不加偏置呢?你把x点和a1点断开当然不行,首先x和a1相接近似于二极管偏置,其次,如果你用相同的直流电压代替,你想想x点不就等效交流地了吗,这两者之间有本质的区别的。