弱问flash ADC中分压电阻串的设计

时间:10-02

整理:3721RD

点击:

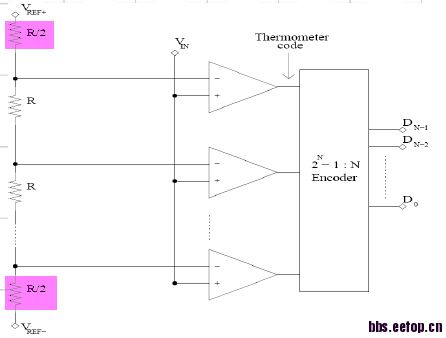

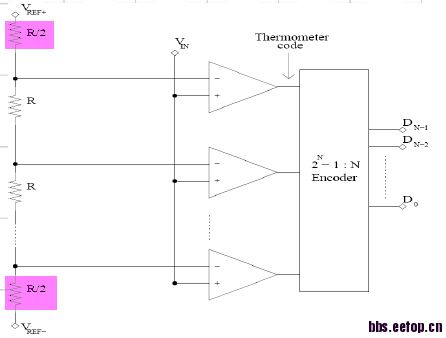

最近在做的4bit量化delta-sigma ADC中要用到一个4bit flash ADC, 似乎很多论文中用到的都是如下图所示的结构:

如高亮部分所示,靠近ref+, ref-的两个电阻为R/2, 而产生比较器参考电压的电阻均为R, 我觉得那两个电阻取R也没什么不妥啊,是出于什么考虑呢? 量化精度?面积?

感觉没想到问题的关键,请高手指点

如高亮部分所示,靠近ref+, ref-的两个电阻为R/2, 而产生比较器参考电压的电阻均为R, 我觉得那两个电阻取R也没什么不妥啊,是出于什么考虑呢? 量化精度?面积?

感觉没想到问题的关键,请高手指点

自己顶一下,不要沉嘛, 高手指点一下呀

以3bitADC为例子。这是一种量化方法,叫做midrise,量化后的输出电压就是这个电阻串得到的8个电压(3bitADC);如果全部用R的话是另外一种量化方法,叫midthread,你会发现这种电阻串除了电源和地,会得到7个电压水平,对于3bitADC,8个数码还差一个,那么就必须使用地或者电源。所以两种量化方法的区别就在量化后输出的电压是否包括电源