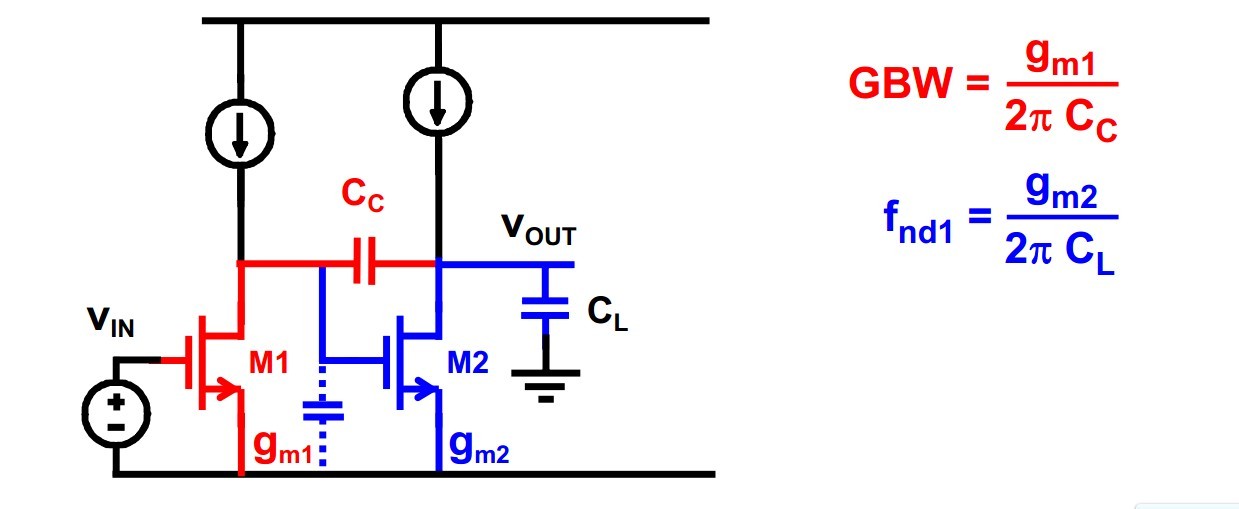

关于Miller补偿中非主极点的疑问。

拉扎维说非主极点是gm2/CL,其中gm2是这么得出来的:高频时CC可以认为短路,这样M2的栅漏短接了,输出结点的等效阻抗就变为gm2了。但是,在一般情况下,CL的取值要比CC大的多,如果频率大到足以短路CC,那么CL也应该被短路才对,这样的话输出结点的阻抗就变成零了,RC时间常数为无穷大!我的分析错在哪里了?

不懂,帮顶。正在看拉扎维Chapter6

阻抗的电阻部分乘以电容部分的倒数是极点频率,要是把阻抗当电阻,那就没电容乘了

也就是说算电阻时不能考虑负载电容?最后再乘以负载电容即可?

将Cc看成短路是为了分析OUT端看进去高频下阻抗的R,而Cc刚好起到了一个反馈的作用,如果Cc》C1,那么可以近似的认为Cc完全将输出端的电压反馈到了输入端,就相当于是短路,所以近似的电阻也就是gm分之一。

而C部分,直接从输出到地的是CL,Cc到地之间还串联了一个相对较小的C1,如果忽略这一部分,就得到了小编图示的公式。

更详细的表达式可以参见Gray的9.4节中的公式(9.33)

你又没明白我的意思

你的理解错在认为短路就是阻抗为0.作者只不过用短路来告诉你并联的哪条支路应该起主要作用。

呃。我觉得我已经说清楚了将Cc近似为短路的原因啊。Cc与C1以及第一级的输出电阻构成了一个反馈网络,高频下并且Cc》C1,得到的结果近似于Cc短路,并不是真的将大的电容都认为是短路。

我问的是CL啊

accept your point of view

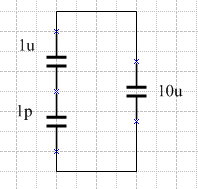

能否这样来理解CL不看成短路的原因:就跟要计算上图中的等效电容时一样,可以将1uF的电容看成短路,而不将10uF的电容看成短路。

个人理解:CL是与电阻并联的,CL不影响看到的电阻的大小,而与电阻串联的的电容才影响电阻的大小。而看到的电容由CL和CC决定,这里CC比CL小很多所以忽略。

8楼回答很有道理,由于Cc和C1分压关系,在M2 gate看到的电压近似等于在M2 drain看到电压

明白了,你是高手!1711064497,扣扣献上,加我哈

说的太对了!

你这个有问题啊,如果真是1u与1p串联的话,那么这相当于一个分压电路,CC上分得的电压与频率无关啊,这样的话无论在任何频率,CC都应该看成短路啊!

我前面说了啊,还有第一级的输出电阻。并不与低频下的结论冲突。

如果C1为0呢,这样只剩CC和CL了,非主极点还是gm2/CL

没错,楼上已经解释比较清楚。我个人也认为,再怎么高频,也不可能等于零。其实输出结点看到的电容式Cc和CL的并联,大小为Cc+CL,所以Cc可以忽略掉吧。这样子就是拉用CL的理由了,因为CL比CC更大,所以它在这里起的作用为主导。

5楼说的是对的,我师兄说过这个高频下的短路是近似,不是真的短路

所谓电容短路不能只看电容的大小,要看和电容相连的R,由RC常数来看带宽,再看对应的频率是不是可以认为是短路的。Rds1要比Gm2大很多

就是的,与Rds1有关,昨晚终于想通了

1/RC,所以主极点可以自己算出来

miller补偿的关键点在于pole splitting

good design的假设都要基于pole splitting的发生