DAC建立时间

时间:10-02

整理:3721RD

点击:

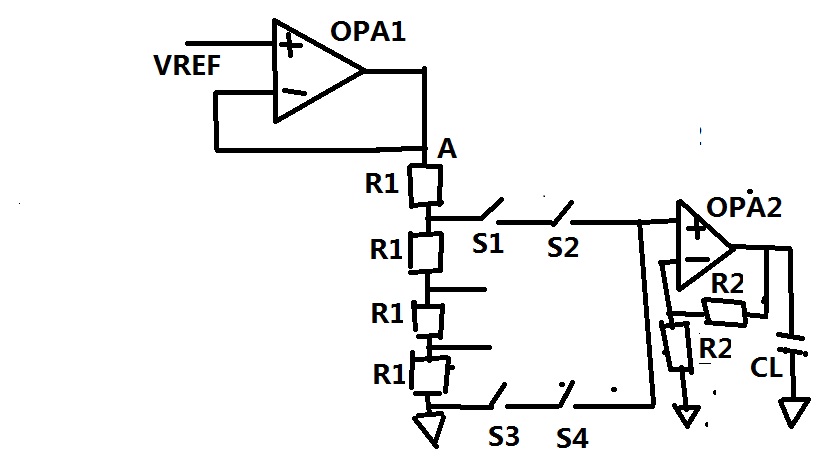

小弟最近在做一个电阻分压型的DAC,10位的,电路结构图如上图所示

电阻串部分由阻值相同的电阻R1构成,这里省略了电阻的个数,用

四个电阻来表示,每一个电阻节点通过两个串联的开关送至输出buffer,

其中输出buffer有12个,即每个电阻节点通过开关后都与12个buffer连接,

从而构成多通道的DAC。

之后信号经输出buffer两倍放大后传送至输出端口,其中负载电容CL为100pF。

请问该种结构能否实现100ns的建立时间(建立精度千0.1%)?

设计时输出buffer应该满足那些指标要求?电阻串电阻值大小如何选取?

在调试过程中,我始终调不到这个指标内,请各位大侠们指点。

注:基准输入电压为1V,每一个buffer输入管栅电容约为5pf。

10bit? 1024个电阻? 1023个抽头?你觉得可行么?

100ns的settle time,也就是10MHz的clk rate, 试试current steering DAC + buffer吧, 100pF loading 有点大

开关分组需要注意,需要分析开关的RC效益,采用最佳的开关路径。

谢谢回复哈

电阻串电阻总和是比较大,即使每个电阻10欧姆,电阻串也有10k多的阻值。现在正处在评估阶段,不知道有无实现的可能,所以在这里请教下各位哈。如果按照RC计算时间常数的话,也是比较大的。

按照你的经验这种结构做这个指标是比较困难是吧?

谢谢回复

开关的译码部分是每个节点都通过两个开关连接到缓冲器的输入端。在该种结构中,如果采用单管开关的话,为了减小导通电阻,开关的宽长比是不是一般都舍得比较大,比如100/1、 80/1这样的?

告诉你不用做了,这样的结构是做不出来的

这个结构谁想出来的?多看看论文什么的,看看人家是怎么实现的

这样的结构简单,但不实用!