请问一个运放的问题,一直没搞明白,书上也没写

时间:10-02

整理:3721RD

点击:

各位大侠好,一直没搞明白一个问题:运放在书上一般表示为一个三角符号,如果做成unit gain buffer,就是输出反馈到负输入端,在这种情况下,如果输出的共模电压在设计时并不等于输入偏置电压,这样是怎么连成buffer的(难道输出dc电压不会影响输入的偏置?)?还有就是loop gain不等于1的情况下,输出也是通过反馈网络直接连到负端吗?

书上关于运放一般都不画偏置电路的,所以这个问题没怎么搞明白,在此请教了

书上关于运放一般都不画偏置电路的,所以这个问题没怎么搞明白,在此请教了

临渊羡鱼,不如退而结网。做一个简单的运放,你就明白了。

的却存在这样的问题,所以设计op的时候,输入范围要尽可能大,而且能够做到单位负反馈

看来你还很动脑筋

这是个问题,

能接成单位增益负反馈的时候,则所以得管子都要处在饱和区,

否则就不能,要严重影响性能的。

主要看运放的输入共模范围,和运放的输出摆幅,看两者有没有重叠的区域,如果有,则可以

输出接到负输入端,否则不能。

运放我设计过,当时虽然没搞明白,但我是设计输出共模电压等于输入偏置,所以可以忽略这个问题的。

原来是这样,醍醐灌顶啊,呵呵,谢谢了

DC相等 估计你的尺寸也是夸张的很

学习中了

这个问题主要是运放的输入输出共模都不是固定死的,是有一定范围地。

而且输出是个高阻,如果是OTA的话,是可以随着输入变地。

正解

我雄堂主!

路过学习学习

输入输出都有共模范围,你仿真的时候可以连接成跟随器的样子 仿真输出与输入 顺便仿真输出级的电流

在输出级电流基本恒定的情况下 输入与输出基本重合的部分就是共模输入

好东西啊,学习下

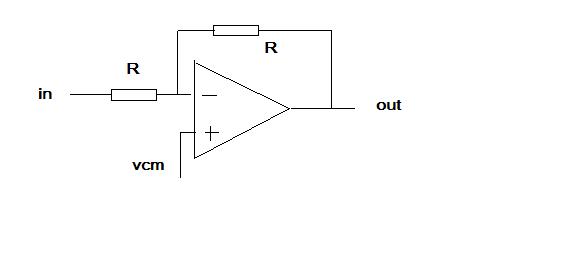

单位增益反馈电路,可以有多种拓扑结构, 不只是你说的 将输出 直接反接到正输入端。

也可以有下面的结构这样 共模输入 有你自己决定

也来学习一下。

输出一般是浮动的,没问题的

有道理

学习学习

路过学习学习

学习了!

学习了

搞个rail to rail ..