正向设计了一个10位50MHz的流水线ADC,却感到什么也没学到

时间:10-02

整理:3721RD

点击:

最近正向设计了一个10位50MHz的流水线ADC,却感到十分郁闷。

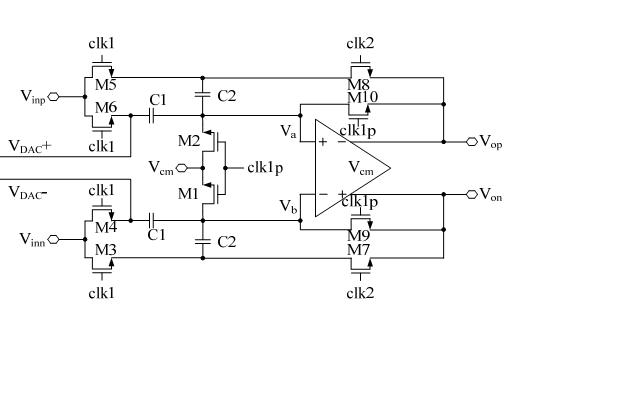

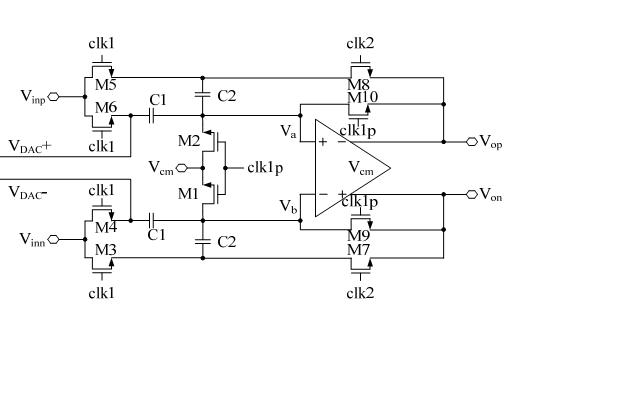

开始,我先在没有采样保持电路的情况下仿真后面的9级,以便确保后面9级正确。这个仿真过程让我很郁闷,尤其是MDAC中开关尺寸的选取。我的放大器有420MHz的带宽,98dB的增益,相位余度77度。

如上图中的MDAC,除了开关M1、M2、M9和M10外,其他都是CMOS开关。这些开关尺寸的选取太费劲了。比如开关M1、M2、M9和M10的尺寸从W=6u,L=0.35u变成W=8u,L=0.35u,结果马上就变错误!M3~M8的尺寸由W=8u,L=0.35u变成W=10u,L=0.35u,结果也是变错。

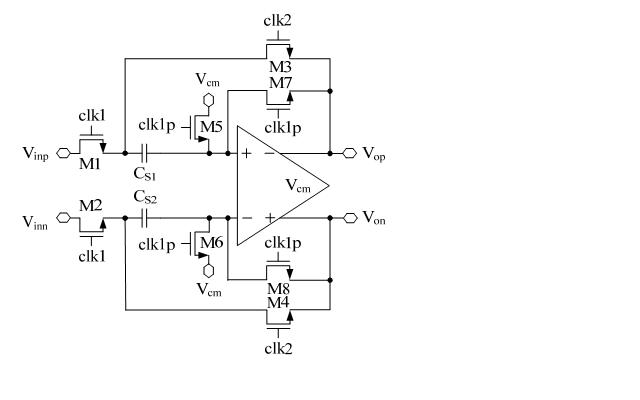

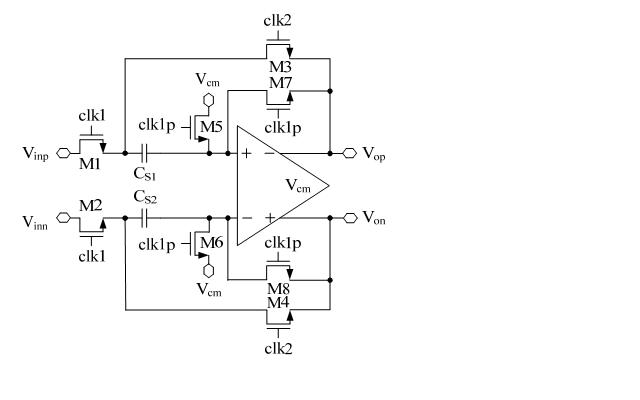

好不容易把后面9级电路调好,又加上了采样保持电路。结果开关的问题又出现了。

上面电路中,开关M1、M2是boostrap,其他都是CMOS开关。同样的现象,M3~M8这些开关的尺寸由W=8u,L=0.35u变成W=10u,L=0.35u或W=8u,L=0.35u变成W=7u,L=0.35u,仿真结果肯定出现错误。而且开关M7和M8不是连接到放大器的输入端,而是连接到共模电平VCM上,结果也会出现变化。

总之,设计了这么一个ADC,现在的仿真结果有9.23bits的有效位,但是这都是“蒙”出来的,主要是还是没有掌握如何设计开关尺寸,感觉拉扎维那本书的第12章给出的公式没有什么实际意义。

不知道大家在设计流水线ADC时,开关的尺寸是如何考虑的?难道也是像我遇到的情况一样,电路对开关尺寸的变化太敏感了。唉,感觉没有学到什么东西啊!

开始,我先在没有采样保持电路的情况下仿真后面的9级,以便确保后面9级正确。这个仿真过程让我很郁闷,尤其是MDAC中开关尺寸的选取。我的放大器有420MHz的带宽,98dB的增益,相位余度77度。

如上图中的MDAC,除了开关M1、M2、M9和M10外,其他都是CMOS开关。这些开关尺寸的选取太费劲了。比如开关M1、M2、M9和M10的尺寸从W=6u,L=0.35u变成W=8u,L=0.35u,结果马上就变错误!M3~M8的尺寸由W=8u,L=0.35u变成W=10u,L=0.35u,结果也是变错。

好不容易把后面9级电路调好,又加上了采样保持电路。结果开关的问题又出现了。

上面电路中,开关M1、M2是boostrap,其他都是CMOS开关。同样的现象,M3~M8这些开关的尺寸由W=8u,L=0.35u变成W=10u,L=0.35u或W=8u,L=0.35u变成W=7u,L=0.35u,仿真结果肯定出现错误。而且开关M7和M8不是连接到放大器的输入端,而是连接到共模电平VCM上,结果也会出现变化。

总之,设计了这么一个ADC,现在的仿真结果有9.23bits的有效位,但是这都是“蒙”出来的,主要是还是没有掌握如何设计开关尺寸,感觉拉扎维那本书的第12章给出的公式没有什么实际意义。

不知道大家在设计流水线ADC时,开关的尺寸是如何考虑的?难道也是像我遇到的情况一样,电路对开关尺寸的变化太敏感了。唉,感觉没有学到什么东西啊!

前仿的话精度有点低吧?

用hspice仿的,加上了.OPTIONS METHOD=GEAR ACCURATE=1 CONVERGE=1 RUNLVL=6语句。感觉精度应该可以了。

感觉精度低了点!

我意思你电路是可以改进的。不是仿真器的问题

您所说的精度是指什么?

请教半支烟:您设计开关时都是怎么考虑的?我的电路对开关的大小太敏感了。比如从W/L=6u/0.35u变成W/L=8u/0.35u,仿真结果就不一样了

结果撮使什么意思?

书上那个模型误差太大了,只能涌来定性汾西活估算。

这说明有很大的改进余地

如何改进?给兄弟指点一个方向啊!

是可以改进

小编继续加油!如果作为前仿结果,9.23位太低了,好歹超过9.8吧;还有各种工艺角过了没?还有,芯片一旦生产出来,如果达不到指标,你有办法找出是哪里出问题么?还有面积、功耗等。所以芯片设计远不止在仿真软件里面跑跑仿真,把指标达到哦