TLV62130降压DCDC使用求助

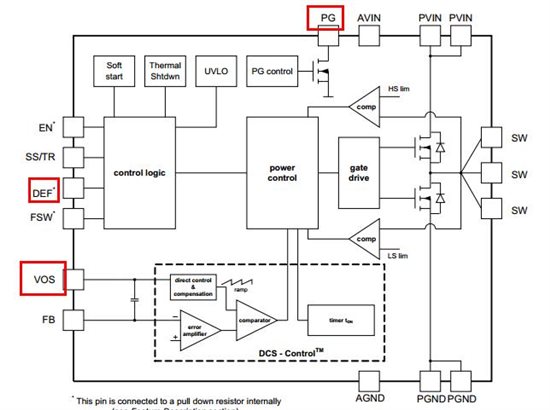

最近有一个项目需要用到输出5V/3A的DCDC,于是选了一款:TLV62130,虽然看了规格书,但是有几个引脚功能还没搞明白,大家了解的能否指点一下,万分感激!谢谢!

不明白的引脚:

1. PG 对于PG引脚,规格书有推荐接 low,也推荐接 high,请问这有什么不同 ? 实际使用接high还是low好?

2. DEF 看不懂该引脚功能

3. VOS 一样看不懂该引脚功能

4. UVLO 这是个什么功能? 芯片内部的

PG 是power good的指示信号,使用时拉高

DEF

The output voltage of the TLV62130 devices can be increased by 5% above the nominal voltage by setting the

DEF pin to High (1). When DEF is Low, the device regulates to the nominal output voltage. Increasing the nominal

voltage allows adapting the power supply voltage to the variations of the application hardware. More detailed

information on voltage margining using TLV62130 can be found in SLVA489.

VOS

Output voltage sense pin and connection for the control loop circuitry.

UVLO

If the input voltage drops, the undervoltage lockout prevents misoperation of the device by switching off both the

power FETs.

Hi Seasat Liu

请问PG引脚接高,接低各有什么不同?我咨询过TI供应商,他说TLV62130接高,而TLV62130A接低,但是他没说两者的区别,麻烦你帮忙指点一下,谢谢!

都是接高,当输出电压异常时,PG引脚就会被拉低,以此来指示输出电压是否在正常

你好,

TLV62130和TLV62130A的不同,可以参考文档:

http://www.ti.com.cn/cn/lit/an/slva644/slva644.pdf

HI

建议通过翻译软件,仔细研读一下芯片的datasheet,这个芯片的datasheet对于芯片脚,更能都描述得非常清楚,而类似于PG功能都是大部分芯片通用或者是类似功能。

1. PG 检测输出是否正常,如输出正常则,PG输出高电平,反之低电平。一般用100K左右电阻将其接在高电位(如Vin,或Vout)具体要看其最大能承受的电压

2. DEF 这是用来调控输出电压范围的,具体可以参看 http://www.ti.com.cn/cn/lit/an/slva489/slva489.pdf

3. VOS 这是用以引入输出电压至芯片内部的管脚,用来进行环路补偿、

4. UVLO 这是欠压锁定,当芯片的Vin低于某一个幅值时,芯片将停止工作,具体的幅值是通过外界分压电阻设定