采用TPS5450做预稳压的数控电源模块

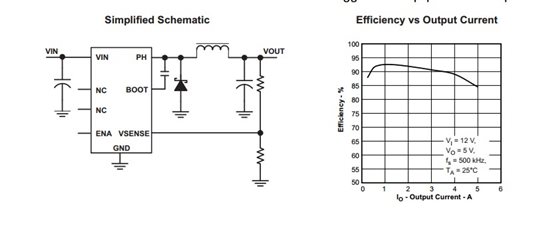

我在工作中做过的一个测试设备项目,其中的数控电源模块要求输出0.1-6V可调,电流0-3A可调,基于体积、效率和成本的考虑,最终决定采用24V母线供电,经过DCDC预稳压后再经线性稳压电路稳压输出。因为最大输出3A且要留一定的余量,因此DCDC预稳压就必须要3A以上的输出能力,能适应24V输入输出3A的DCDC电源I很多但3A以上就相对较少了,经过筛选最后选择了TI的TPS5450做预稳压电路,(TPS5450详见附件,也可以去TI官方网站下载)该IC最大输入电压:36V 最大输出电流:5A,外围电路非常简单,标称效率:输出3A以内可以达到90%以上。见附图1:

图1

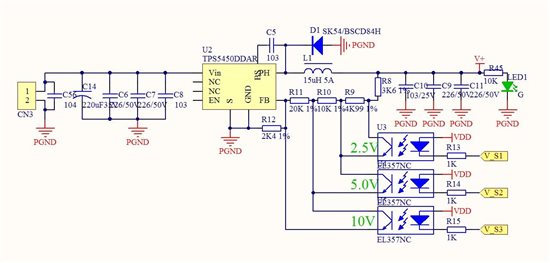

最终应用的预稳压电路如下图2所示,图中通过V_S1,V_S2,V_S3 的3个IO端口有序组合分别得到约:3V,5.5V,8V,10.5V,13V,15.5V,18V,20V 。 8种预稳压电压值,其中V_S3 控制端口在该项目应用中没有用到仅作为扩展的备用端口。输入端采用高频低阻电解电容加瓷片电容组合滤波,C5自举电容参考典型应用电路设计,续流二极管采SK54 40V 5A肖特基,L1电感采用CDRH127封装 15uH电感。

图2

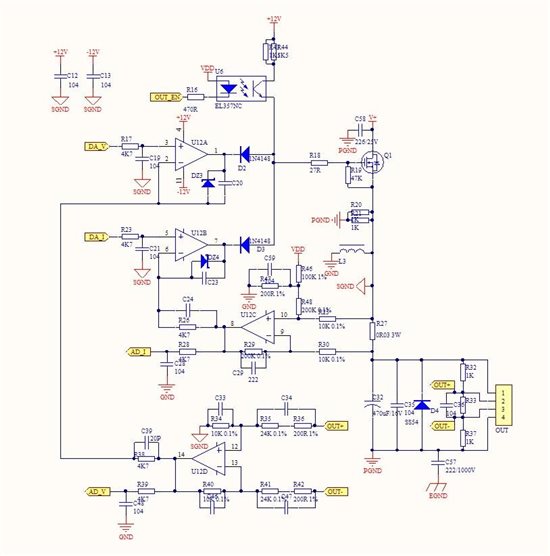

后级线性稳压电路如附图3所示,后级线性稳压电路输入取自TPS5450 DCDC电路的输出端。预稳压值由设置电压和恒流状态而定。

图3

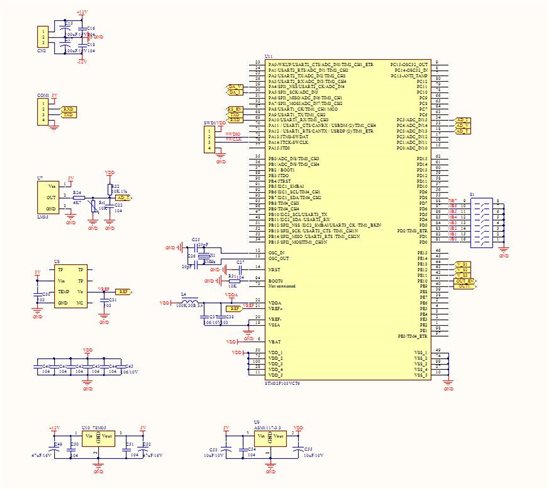

控制电路如附图4所示,主要采用STM32F103 来控制,电压电流设置通过串口设置,同时可以读回实际输出电压、电流、功率等工作参数。为了保证电源模块输出电压准确度,模块采用了0.2%精度,20ppm/℃ 电压基准,同时该模块生产时都进行参数校准,校准后输出电压电流可做到约0.2%的精度。

图4

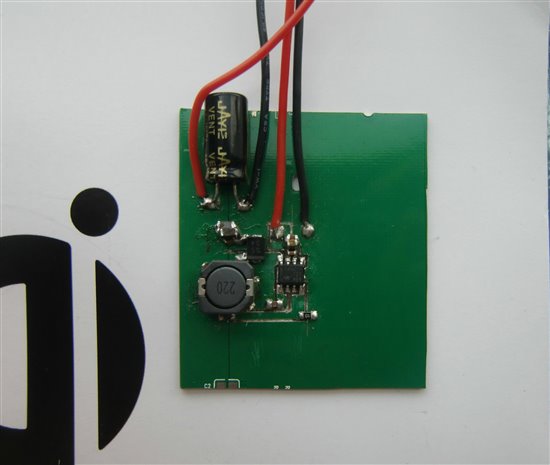

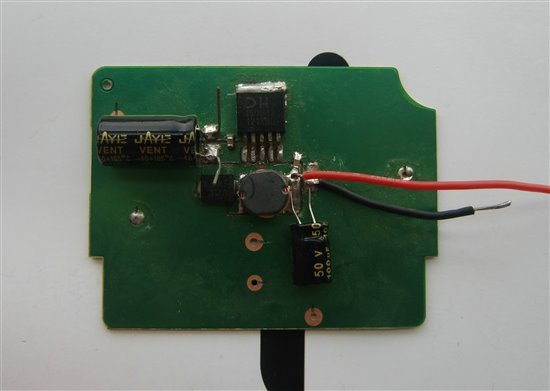

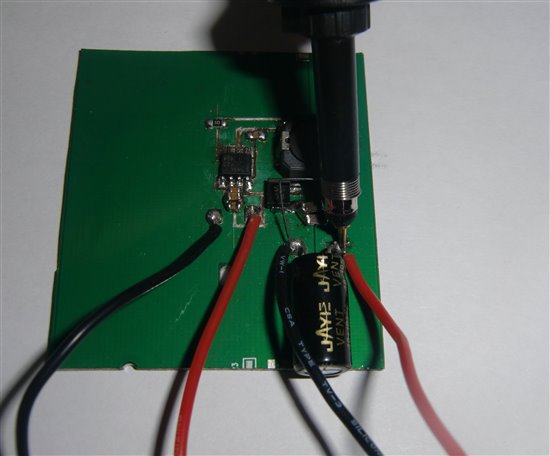

应用的电路已经简单介绍了,再补充一点实际电路验证、应用及一些小经验。刚拿到这颗IC时首先置疑的自然是这颗IC是否能用到实际的项目中,最简单的想法是先把电路搭起来试试看。如果要设计原理图和PCB板再去打样板验证,周折一通费时肯定不少,而TPS5450外围器件也非常少,于是想重操旧业用“刀刻法”做个简单的DEMO板。先找了一块有大面积空铜皮的费PCB板,裁剪了一片约50*50见方的小片,将IC及主要元件在脑海中大致的排了一下位置,将IC直接压在板上用铅笔简单画出引脚位置和PCB走线时要分割的铜皮,然后就是刀刻作业了。刻PCB板我一般是用小介刀的背面来割的,用刀刃割一般就先割两条线,然后把中间多余的铜皮挑起撕掉。整个PCB板刀刻过程大约半个小时左右就完成了。最后焊接好元件就是附图5的样子了。图中元件和最终的元件还有点小差异,因为当时手中没有15uH的电感就用22uH的代用了一下。其实这种刀刻法做一些简单的试验板还是挺方便的,顺便再发一张以前手工雕刻的试验PCB怀念一下,见附图6。

图5

图6

手工作的板子测试下来效率如下:

| 输入电压(V) | 输入电流(A) | 输入功率(W) | 输出电压(V) | 输出电流(A) | 输出功率(W) | 效率(%) |

| 20 | 0.449 | 8.98 | 8.331 | 1 | 8.331 | 92.77 |

| 20 | 0.897 | 17.93 | 8.331 | 2 | 16.62 | 92.69 |

| 20 | 1.372 | 27.44 | 8.292 | 3 | 24.87 | 90.63 |

测试照片见附图7-9:

图7 :输出1A

图8 :输出2A

图9 :输出3A

今天先更新到这里,未完待续。

TPS5450这颗IC比较简易,外围器件比较少;我之前也有使用过,但是要注意如下几点:

(1)环路参数及输出端电容的设置:输出电容的ESR会极大的影响电路稳定性,这个可以通过带重载时测试开关结点的波形验证;如果没有设置好,容易出现大小波的情况;

(2)散热的设计:TPS5450标称是可以帯载5A持续电流,但是如果散热做不好的话,会导致IC过热,内置的mos管内阻增加,从而过流保护提前动作,远达不到标称的5A持续负载;

兄台后续可以把这一块相关的波形测试图贴上来,和大家一起分享下,TKS

谢谢您的分享,您提及的2点经验非常好,给我的分享帖提升了技术含金量。

接下来打算再补充PCB布线及一些元件选取个人心得,您提及的波形图我也会在下次更新是补充上。

最近工作有点忙,所以更新没那么快。今天主要讲一下PCB布线注意事项。

这类DCDC 电路PCB布线抓好以下4个重点,基本上电路就没问题了:

1,分清楚电路中的大电流回路,尽可能提供宽裕的PCB铜皮走线;

2,分析电路中大电流的AC回路(大的电流变化回路),尽可能缩短这个回路走线长度;

3,处理好IC的散热;

4,尽量减少PCB铜皮压降对采样回路的干扰;

下面以TPS5450简化电路来做分析;

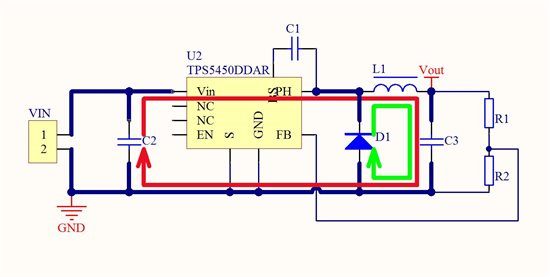

附图: TPS5450简化电路

1,“分清楚电路中的大电流回路,尽可能提供宽裕的PCB铜皮走线”

可以看出图中蓝色粗线部分电路为相对的大电路回路,实际布线中尽可能用较宽的铜皮走线;

2,“分析电路中大电流的AC回路(大的电流变化回路),尽可能缩短这个回路走线长度”

图中红色箭头的回路和绿色箭头的回路有大的电流变化,要尽可能缩小回路长度;

3,“处理好IC的散热”

这颗IC因为内置了功率MOS,那么它主要消耗的功率:I*I*R (电流的平方乘以MOS内阻)这部分功耗主要以产生热量来消耗掉,那么散热就得处理好了,可以通过大铜皮来散热也可以加散热片来辅助扇热;

4,“尽量减少PCB铜皮压降对采样回路的干扰”

图中C3负端到U2的GND端,有大电流流过,那么在这条GND铜皮上就会有电压降,而且这个电压降会叠加到R1和R2构成的电压采样回路,这时候输出电流的变化就会直接影响到电压反馈,因此最好的处理方法就是将U2的GND引脚单独尽可能靠近C3负端,或者单独连线到C3负端。

如果您想做的更好更专业那还可以考虑以下几个方面:

1,尽量减少铜皮寄生电容对信号回路的干扰,比如增大信号线路与大电流变化的回路之间的距离;

2,减少信号回路的线径,(线径越宽“天线效应”越强);

3,高频滤波电容布局优化;

等等-------

今天就先写到这里,上次说的输出波形还没时间去处理,只能下次更新了。

不错,拿出来显一下

建议增加一点:关于芯片的控制地与功率地的布局布线设计;

对于PCB走线来说,有趋势功率回路,高频变化。除非是热很散出去。我一般设计就是铜皮的宽度刚够用就好,不追求过宽,过宽的铜皮有可能导致较差的EMI干扰。

呵呵,提的不错,确实EMI方面铜皮可以当做“接收天线”,也可以理解为“发射天线”。对于高频干扰源来讲,越宽的铜皮就像增益越强的“天线”。

我们当然也可以将所有铜皮当天线来分析,但是这样显然不具备效益。因此最好的分析干扰源的轻重比例来分别对待(也就是管理上常用的2:8原则)。在本例的实际应用中,高频成份最多干扰最强的就是IC第8脚(PH脚)与电感相连接这段铜皮,因此这段铜皮尽可能的短。而其他的铜皮相应对EMI影响弱一些,对布线可适当放宽一点。

有没有测试数据,纹波和动态响应方面的,和线性稳压比较,有哪些优势以及劣势?

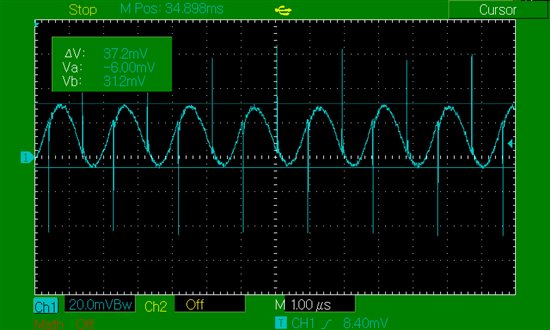

今天简单测试了一下输出纹波。纹波测试点取输出电容引脚上,如附图1所示:

附图1

示波器探笔处理如下图:

附图2示波器探笔测试纹波专用配件

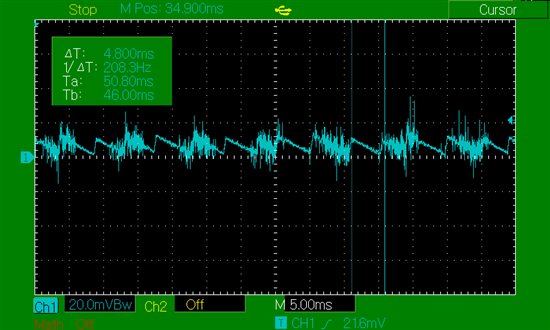

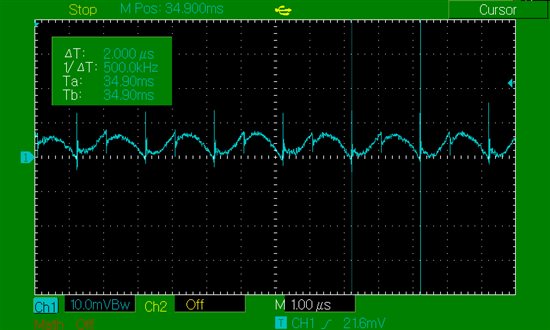

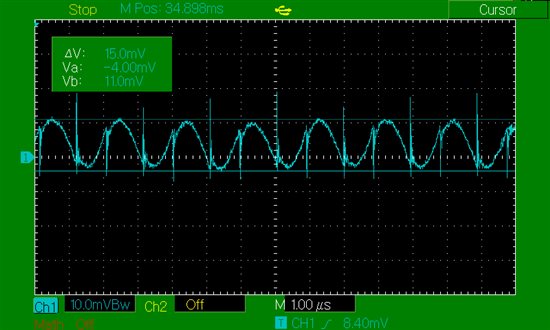

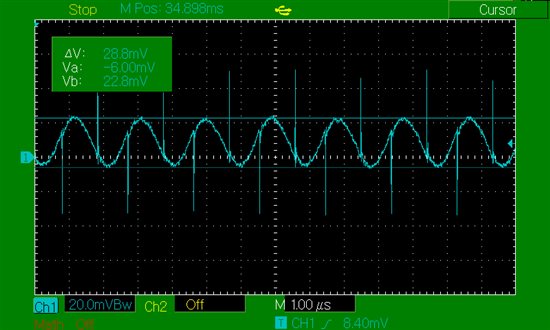

测试空载、1A负载-5A负载输出纹波示波器抓屏如下:

空载时纹波

输出1A时纹波

输出2A时纹波

输出3A时纹波

输出4A时纹波

输出5A时纹波