DC/DC降压稳压芯片中的相关参数疑问

时间:10-02

整理:3721RD

点击:

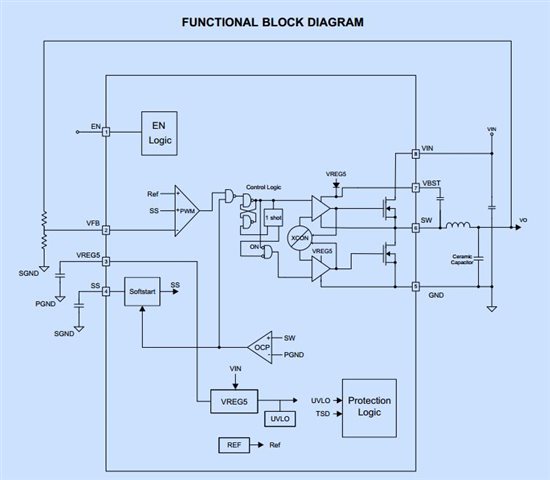

在TI的DC/DC降压稳压芯片中,输出为Vout=0.765x(1+R1/R2),其中0.765应该是内部的Vref,以TPS54327为例,其内部功能框图如下:

疑问1:Vref的大小在设计时需要考虑哪些因素?高一点,还是低一点,其依据是什么?

疑问2:欠压保护功能中Vreg5的电压低于3.75V会触发欠压保护功能,设定为3.75V的考虑因素有哪些?

这些参数的选取规则数据手册中没有提到,希望能得知其中缘由,或应该参考哪些资料可以获知?

1.Vref电压是有芯片内部的带隙基准源产生的,通常都在0.7V以上。在设计电路是您最需要考虑的是Vref的精度。

因为此基准源精度会直接影响到您VOUT的电压精度。此外Vref决定了VOUT的最低输出电压,如果您设计的VOUT低于VREF,则此芯片无法满足您的设计需求。

2.UVLO欠压保护电路,是为了防止在输入电压过低的情况下,芯片内部电路工作不正常而导致外部输出错误。

在设计时,您也可以通过两个分压电阻连接到EN来改变整个系统的最低工作电压。

楼主,楼上已经叙述地很详细了,补充一些,

1. 关于Vref,一般芯片内部是固定已经做好的,你选中了芯片,它内部的Vref也是固定的。至于高点和低点,区别应该就是空载时候芯片本身的损耗了。对于Vref,更多需要考虑的还是最低输出电压是否能满足,Vref的误差,以及Vref随着温度变化产生的误差大小。这个在datasheet时而都有写的。

2. 欠压保护,从芯片级来讲,就是保证芯片内部的逻辑电路、基准源等都能正常工作,从系统级来讲,保证系统电压在低于多少时,不再向后级供电,那么可以如楼上所讲,使用分压电阻来设置系统的欠压保护的电压。