请教 关于 Gate Drive Transformer 的问题

时间:10-02

整理:3721RD

点击:

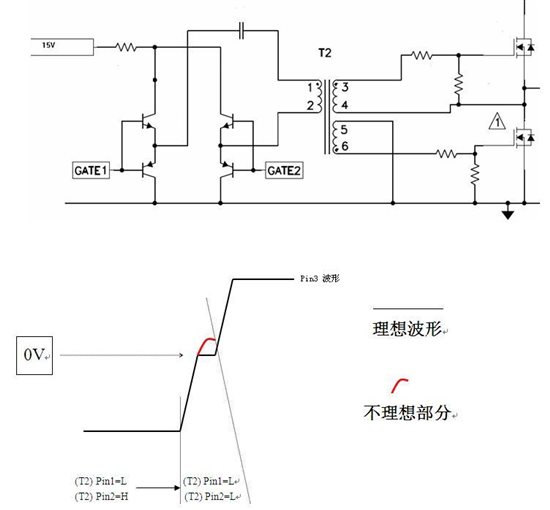

上图 波形为(变压器T2 )Pin3 的输出,当 变压器T2 Pin1为低,Pin2从高变低。

也就是在死区的时候,正常来说应该维持一小段0V,但实际波形(红色)却微微抬高,变压器T2性能没有问题(电感量和尺寸)

系统可以工作,但红色那一小段波形会冲到2.8V左右。

所以想问一下此问题有什么改善方法么?

应该和三极管的结电容有关系。请问楼主,Pin3指的是什么芯片?

我们可以来分析下。

变压器T2

按照参考设计给的电感量,变压器设计上应该没有问题。

我个人感觉是 电感特性 造成的反向电动势,也就是本来Pin2=H Pin1=L,当Pin2=L时为了维持之前的电流会产生一个反向电动势(Pin1高电平),从而使次级的Pin3 产生高电平。

很多Ti相关的参考设计都用的此电路,所以不清楚自己什么地方没有注意。

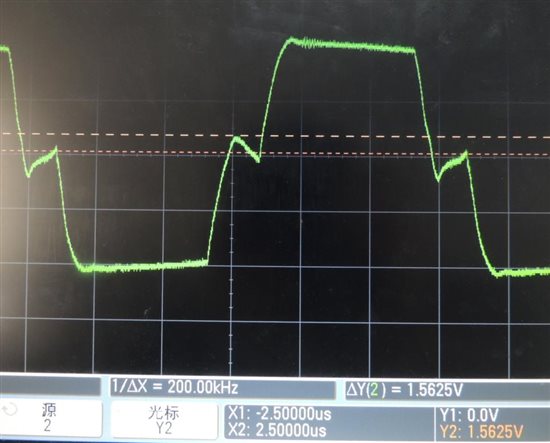

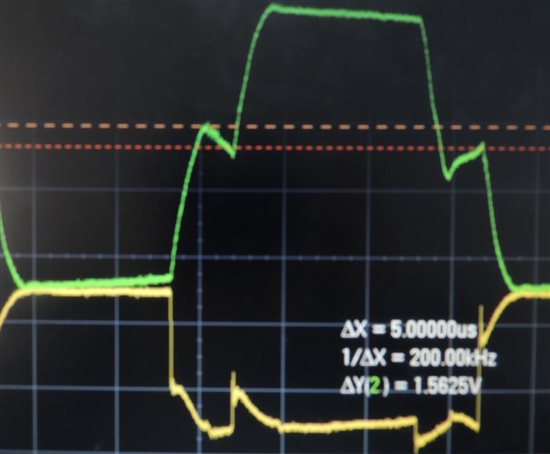

这是实际的 Pin3波形(示波器探头的地接pin4)

绿色:Pin3波形

黄色:Pin2波形

自己顶一下

楼主你好,请问下GATE1和GATE2的波形是怎么样的,有死区时间吗?

黄色 波形 就是GATE2 的

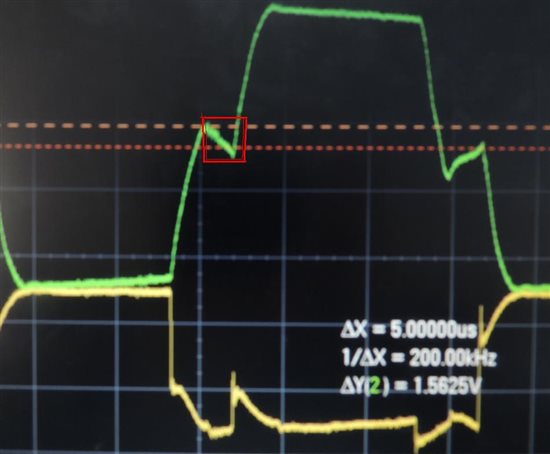

有死去时间,绿色波形中红色方框就是gate1 gate2在死区时间Pin3的输出,应当是0V,但现在出现了过冲,1.5V左右。

Vgs的阈值是3V左右,不知有没有问题。