tps28225 Ugate波形问题

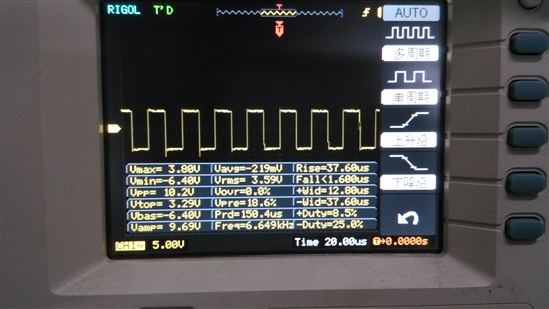

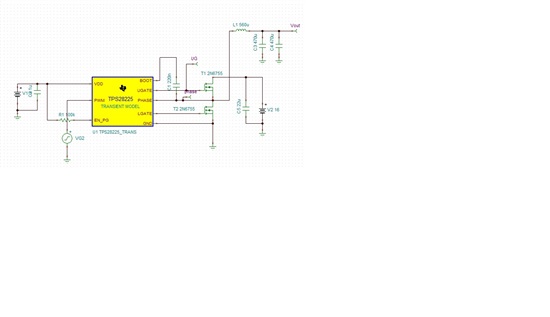

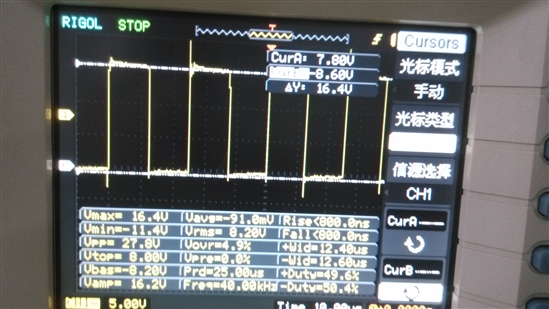

本人最近用TPS28225做一个同步buck电路,电路图如下,供电电压7.2V,输入电压12V,mos管IRF540,PWM波幅值3.3V,占空比为50%,直接输入方式,下图为Ugate波形 上图为Lgate输出波形

:

:

自举电容用过2.2uF、10uF电解电容0.1uF瓷片电容,Ugate波形差不多都是那样,请知道的人指点一下,到底是什么原因。

正常现象!波形是对的。

亲是用功率地为参考测的高边驱动。这是的波形实际有两部分组成:栅驱动信号和半桥输出电压。亲测到的是两者之和。所以;幅值比较高。

由于高端MOSFET开通是完全受控的;而关断后;电路处在自然过渡过程,电压变化率受负载电流及其它分布参数影响,所以;波形上升沿很犀利;而下降沿的顶端部很陡;下半截是自然过渡,所以比较缓。

因此;虽然波形总体有点三角波的感觉;但是是对的。

不应该适合低端互补的吗?而且输出电压完全不符合要求只有0.5V左右,调节占空比对输出电压没有很大作用。

只要不短路;是否互补,对输出没有本质影响,就波形而言,完全正确。

至于亲觉得哪不对,应该从输入;输出和占空比同时比较。只强调一个输出不对,没有任何意义。

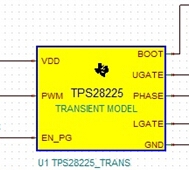

楼主,你的这个器件仿真是怎么画上去的?

谢谢你的回答,今天输出电压波形都正常,我是在使能端串了个100K电阻,以及断开了功率地和信号地断开的情况下正常输出的,datasheet并没有强调这两点,请问是为何呢?而且7.2V供电容易烧芯片,我们用的是5V供电。

估计你用的是TINA了 你可以在自带例程里面找到这个芯片的其他仿真电路 然后ctrl+C ctrl+V到新文件框就可以用了 注意右键是没用的 没有例子也可以到官网找得到的!

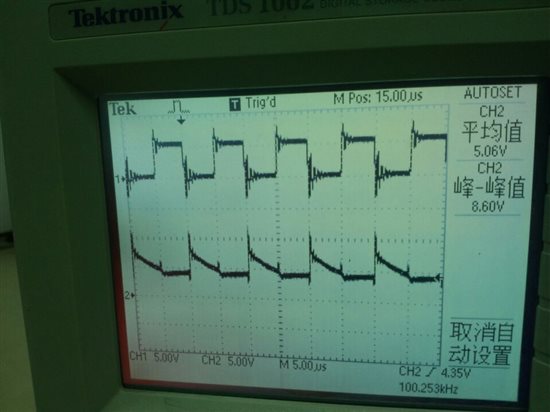

不是的,我想仿真下tps28225,可是不知道该用那款软件,出了tina。你这个图是仿真电路吗?顺带问一下,我最近也搭了一个和你一样的电路。boot端对地电压的波形图是这样的:

上面是输入的pwm,你们的波形也出现过这样的吗?今天,你们的正常的波形是什么样的呀?能给我看看么?

我那个图是TINA的仿真电路图 是可以正常工作的。这个芯片只适合做BUCK,我们的功率地和信号地是分开的,我们的高端和低端测波形都和PWM波一样规则。你的BOOT脚波形是那样,估计你的高端测MOS管没有正常导通吧,估计你的高端测波形也不好,具体什么原因我也不是很清楚,可能是自举电容,我们用的是2.2uF电解并104瓷片,电容尽量靠近芯片。这是高端测对地波形:

如果供电电源与输入电源的地在之前已经供在一起了,就不要在电路中将这两个地又共一遍,刚刚找出之前烧片子的原因了。

请问1号脚幅值只有毫伏级

1号脚正常是输出低电平Vin 高电平 Vin+vdd-0.7这是按我自己的电路来说的,不知道你的电路时怎样的。

好漂亮的波形!我的高端侧波形的确不好,并且有杂波。

信号地和功率地能分开么?一旦隔开,我觉得vgs就不容易保证了。你们是怎么做到呢?能大概说说思路么?

因为我们的两个电源的地之前已经共在一起了,如果把整个系统的地再共一次,估计有干扰!

好的!我就说嘛,从原理上讲,ugate的自举电容是上门导通的核心,若要加隔离,这个自举电容就没法用了。我的ugate也输出方波了,只是间隔数个完整的方波后,有一个很丑的缓慢上升的曲线,像是电容充电一样。我觉得pwm波生成器也非常关键,我用SG3525来做的话,ugate就没有过完整的方波,整个波形都在闪动,很多尖刺。你们用什么生成pwm的呀?

我们用单片机产生的40KPWM 你所说的加隔离是什么意思啊!

我说的隔离是指电源地和信号地完全隔离。