POE(TPS23754)设计输出干扰

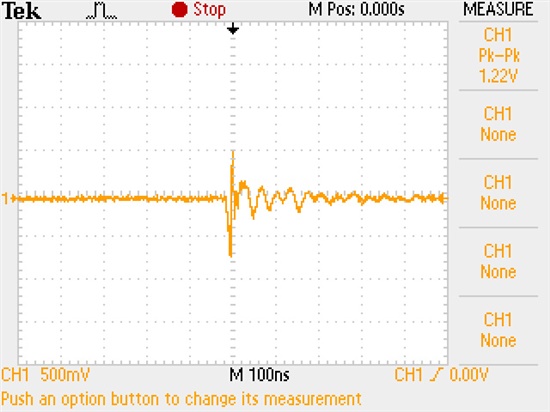

现遇到一个较棘手的问题。用TPS23754 设计FLYBACK式DC12V输出,变压器JA4378-AL(线艺),输出出现跟开关同步的波纹干扰(输出已加滤波电容220UF)

此干扰与开关的上升沿和下降沿同步。同时也请教的深圳的TI技术支持工程师,他的解决方案如下,

此干扰与开关的上升沿和下降沿同步。同时也请教的深圳的TI技术支持工程师,他的解决方案如下,

A. 将C16由330pF改致2.2nF~4.7nF;

B. Q1的驱动极,去掉D5及Q2,让R9直接连至Q1的G极;

C. 减小R1,可在22K~39K之间调整下,另请留意在减小R1时须提高R1的功率等级,如用多个1206电阻并联;

D. 输出端并两个1uF/0.1uF的X7R贴片电容,减小输出电容ESR以加强滤波效果。

从您发过来的图来看,该输出纹波可基本确定是由于次级续流管的上冲引起的(续流管下冲及MOS的上/下冲均还OK)。

对于消除该过冲,续流管D6上的RC SNUBBER(R10,C16)即为起该作用的,所以如果在目前不改PCB及换管子的前提下,调试该线路应该会是首要手段。

调试时,在昨天的基础上,建议继续增加C16的容值(最大8.2nF)及R10的的阻值(最小1R)来看相应变化。(此时可直接测试输出端纹波及D6的AK端电压波形来量化改动后D6的上冲及输出纹波如何变化),同时,做上述改动会增加二极管损耗,请同时留意其温升是否在允许范围。

另外,此处LAYOUT及D6的选型也会对该过冲及输出纹波产生影响:

- LAYOUT上:请看下从变压器T1出来至D6的连线及D6至L2的连线,尽量缩短其长度及减小宽度至合适值会有帮助(不重新LAYOUT的情况下,可实验将元件焊离PCB再飞线连接)

- D6选型: 看了下您现在用的D6-PDS760的规格书,但没找到其反向恢复时间的数据,建议您看下手头上有没有反向恢复时间更快的二极管(如反向恢复时间<15nS,且耐压无需60V,以您现在应用,Vo+Vin/n应<30V,在有高过冲的情况下50V足够,如后续过冲能完全压下来,40V即可)-----------------------------------------------------------------------------------------------------------------------按照上述方法试过,均未改善,请问其他工程师有什么更好的解决方法?

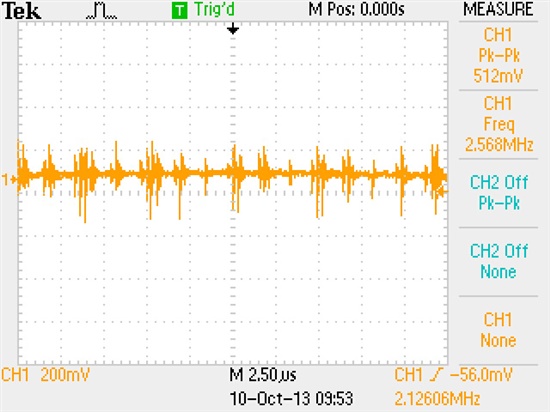

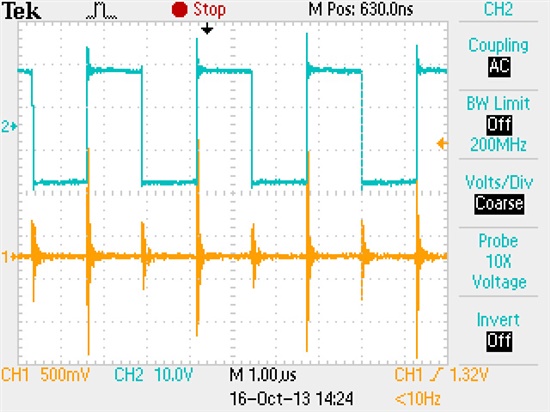

上图是测的D6 K端(CH2)与输出的DC12V(CH1)的图形。开关频率电阻用的是69.8K,输出频率理论250K,实际示波器测的是400K,去掉D5、Q2 GATE直接通过R9电阻驱动MOS FDT86102(FDT86102代替FDS2572)后,不能正常工作。请问这两种情况主要什么原因造成?

上图是测的D6 K端(CH2)与输出的DC12V(CH1)的图形。开关频率电阻用的是69.8K,输出频率理论250K,实际示波器测的是400K,去掉D5、Q2 GATE直接通过R9电阻驱动MOS FDT86102(FDT86102代替FDS2572)后,不能正常工作。请问这两种情况主要什么原因造成?

原理图SCH.PDF中R31、R19是NC。

驱动电阻太大了,参考设计中给的是10欧

哪一个驱动电阻?我主要参考PMP5236的设计!