关于漏极开路(open drain )的具体工作细节及用法。

我现在在设计电路,好多产品都是你们家TI的,也都是按照你们的tpyical application的接法接的,但是关于用你们I2C接线时候,引脚是漏极开路一定要用上拉电路,,具体为什么我不是很清楚?能否详细指点下

漏极开路(Open Drain)只能输出低电平和高阻状态两种状态,若需要高阻状态有高电平状态,则需使用外部接上拉电阻.

i2c 总线通常需要 OD 门驱动外加上拉电阻. 以实现多路驱动和竞争仲裁机制.

你也可以从以下这个角度来理解这个问题:

对于开漏输出的结构,当mosfet导通时,i2c引脚得到的电压是与地短路的(忽略mosfet的导通阻抗),此时得到的输出电压为0,若没有上拉电阻,此时漏极接的上拉源也会对地短路(忽略mosfet的导通阻抗),那么会有很高的电流流过mosfet,甚至烧毁mosfet,所以当输出0时,上拉源的作用就是限流,其大小也决定了其偏置电流消耗。

当mosfet关闭时,此时i2c引脚的输出电压与漏极供电电源短路,此时输出的信号就是固定的上拉电源VCC,此时是可以输出逻辑1的,上拉电阻在实现逻辑1的作用就是起到保护的作用,如果后端的负载损坏,那么此时这个上拉电阻就可以保护供电电源不会过流。

综上所描述,上拉电阻最基本的作用是保护在实现逻辑0时不会过流,实现逻辑1的时候能够有负载短路保护的功能,此外还可以增加电路抗干扰能力。

如何理解上拉电阻具有一定的抗干扰能力?如果没有上拉电阻,那么信号的1是直接等同于供电电源的,如果供电电源有扰动,那么这个信号会直接影响到输出的逻辑1的波形。有了这个上拉电阻,得到的逻辑1实际上是上拉电阻和后端负载输入阻抗(理想情况下视为无穷大)分压得到的,那么噪音信号通过这个分压能够适当的衰减,对于噪音信号就具有一定的抑制能力。

以上谢谢!

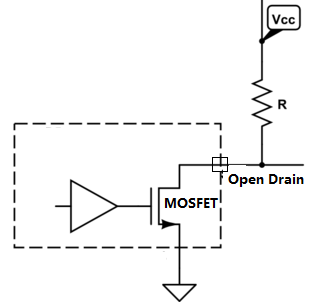

漏极开路(Open Drain),顾名思义指MOSFET的漏极开路,简称“开漏”,其结构如附图所示。分析如下:

(一)如果没有上拉电阻(附图的虚线方框外),当MOSFET导通时,输出直接接地,即输出电平为0;当MOSFET关断时,输出悬空,此时输出电平状态未知,如果后面带一个电阻负载到地,则输出电平会被拉到0,无法输出高电平。

(二)因此,为了输出高电平,需添加上拉电阻。当MOSFET导通时输出电平为0;当MOSFET关断时,理想情况是输出高电平等同于外部电源VCC,实际情况是输出高电平等于上拉电阻与MOSFET漏源电阻的分压。

(三)上拉电阻的电源电压决定开漏输出电平,这样可以实现任意电平转换。可以解决I2C通信时主机与从机的通信电平不匹配的情况。

(四)可以将多个开漏输出连接到一根线上,形成“与逻辑”,满足I2C一主多从、关断总线占用状态等。

我回答你的问题了吧?

谢谢Mingwu的总结,楼主看答案时注意我说的没有上拉电阻时可以输出高电平 是指的没有上拉电阻,电源VCC连接到MOSFET的漏极(当mosfet关闭时,此时i2c引脚的输出电压与漏极供电电源短路,此时输出的信号就是上拉电源VCC,此时是可以输出逻辑1的),Mingwu说的输出悬空状态是指的没有上拉电阻,不给MOSFET的漏极供电,此时上拉电阻的位置是空缺的,电源Vcc不接到MOSFET的漏极,输出为高阻的状态。以上谢谢!

谢谢 指点啊 谢谢

漏极开路是相对push - pull 门来说的。

漏极开路门可以直接并联实现线与,就是多个门直接并联在一起。

而push-pull门,就是上下两个晶体管的那种,是不能直接连在一起的。