LMK04828 PLL2无法LOCK

时间:10-02

整理:3721RD

点击:

TI工程师,

你们好!我在配置LMK04828时,使用单PLL模式(PLL2),PLL1 powerdown.PLL2的鉴相频率设定为100M!通过示波器观测时钟有输出。但是Status_LD2引脚(已经配置为pll2 lock标志)为低,读取0x183寄存器,寄存器值也为0x00,表明PLL2未锁定!

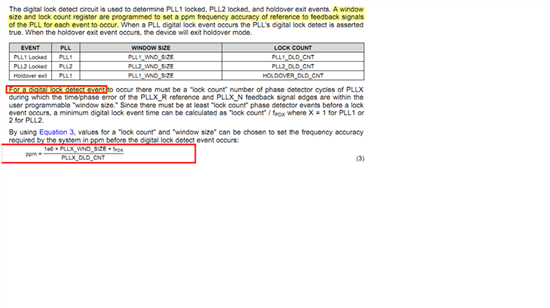

反复看datasheet,看到LOCK信号与PLL2_DLD_CNT设定有关.

设定50ppm,得到PLL2_DLD_CNT为1850,不知道这样设置是否合适.

还有环路滤波参数选择会影响PLL2 LOCK ?

配置文件见附件(去除后缀.txt即为配置的mac文件)

期待您的回复!

PLL 是否锁定是根据相位误差来判断的,当判断到相位误差小于一个阈值的时候,就认为锁定了。 PLL 未锁定,输出的信号时钟的抖动会比较大,建议修改环路参数,环路参数应该可以使用对应的软件生成。

你好,请帖下原理图,codeloader配置截图包括参考频率,鉴相频率等,谢谢!

最简单的诊断方法是将PLL2_LD_MUX设置为PLL2的N和N/2及R和R/2,看下频率是多少,谢谢