ADS8320采样率与DCLOCK关系

时间:10-02

整理:3721RD

点击:

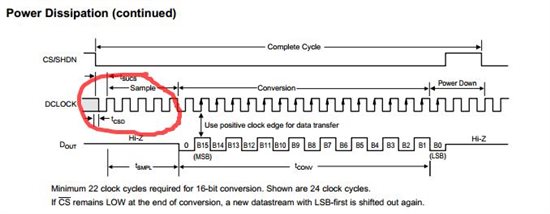

请教一下TI的工程师以及社区会员们,我看了一下数据手册(The external clock can vary between 24 kHz (1-kHz throughput) and 2.4 MHz (100-kHz throughput).).以及附件图片, 得出结论是不是ADS8320的采样率是/CS拉低后,DCLOCK前5个周期信号的频率是fclk,那么采样率fsample=fclk/24.

前面sample 时间是5CLK,中间转换时间16 CLK。 Power down时间为4CLK.

您的结论fsample=fclk/24是没问题的。