tlk10022配置问题

我在使用tlk10022做4路2.5G信号(CML)转10G信号的传输,要求芯片不对传输的数据进行任何处理(不编解码,bit interleaving模式,training sequence),在配置时将RX_LANE_MARKER_EN设置为0、TX_LANE_MARKER_EN设置为0(关闭收发端marker search/replacement character),将HS_ENC_BYPASS、HS_DEC_BYPASS、LS_ENC_BYPASS、LS_DEC_BYPASS都设置为1(关闭高低速侧8B/10B编解码),将RX_BIT_INTERLEAVE、TX_BIT_INTERLEAVE设置为1(使能收发通道bit interleave),其它都使用默认配置,使用读寄存器,可以看到数据正确写入寄存器,输入时钟为125M,上电后链路未通,我的接收端未收到信号,不知是否还需要进行其它设置,或者是否有什么调试技巧?

Hi manU,

你可以在下面的链接下载TLK10022的开发板GUI,通过GUI你可以根据你的应用来得到相应的寄存器配置,然后根据配置在自己的单板上进行调试。

http://www.ti.com/tool/tlk10022evm

您好,

感谢您的回复,虽使用了GUI,但是有些地方还是不懂,我在读取寄存器信息时发现ls_tx_fifo_overflow位为高,根据手册解释,是txfifo溢出,对txfifo使用的是默认设置,不知什么情况会造成txfifo溢出?另外LS_TXFIFO_DEPTH_SEL默认值为0,是否表示数据未存储到txfifo中?请帮助分析,谢谢!

建议采用下列调试方法:

1.在高速端和低速端均采用外部loopback 。

2. 使能内部PRBS(pattern generation and verification),高速端和低速端均使能,pattern 形式自己选(都差不多)。

3. 时钟配置正确。

4. 发送端:可以增加swing和调整De-emphasis的设置(有利于增加传输距离)

5. 接收端:可以调整适当EQ

6. 最后进行BER test 来判断低速端和高速段是否正常联通。

您好,

感谢您的回复!

按您所说,采用自回接法,可通过芯片CLKOUT测出时钟信号输出。我使用的时钟输入信号是125M差分时钟,高速侧PLL20倍频,高速侧使用Full Rate 模式,根据手册公式,高速侧线速率为125M*20/0.25=10G;CLKOUT使用默认设置,根据CLK_CONTROL寄存器说明,CLKOUT来自Ch A HS recovered byte clock,并且Divide by 4 ,由于高速侧SerDes为20:1,那么CLKOUT是否这样计算呢?Ch A HS recovered byte clock = 10G / 20=500M,CLKOUT = Ch A HS recovered byte clock / 4 = 125M;如果测得 HS recovered byte clock是否说明高速侧有正确的通信在进行呢?

你好,

是的,观察接收端 recovered clock output 也是判断是否通讯正常的简便方法。

高速侧时钟输入输出配置都没有问题。但是请注意时钟输出通道(channel A)应该也是你采用loopback接法的通道才对。

您好,

非常感谢您的解答!

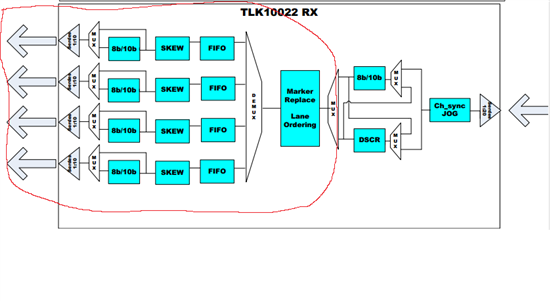

如上所述,我观察到正确的接收端 recovered clock output,是否意味着可以将问题初步定位在低速侧接收上,如图红线圈定部分?

你好,

对,同样的方法,你再在低速端loopback, 然后 Clockout 也选择相应的通道,观察是否有正确的时钟输出,如果有就说明低速端应该也没有什么问题。

您好!

低速端loopback是指将两片高速端相连的SerDes芯片其中一块低速侧tx,rx连接上么?如果这样的话,我的电路板是无法实现的!谢谢您的解答!

是的,如果外部连接不方便的话,可以采用内部loopback模式,将寄存器HS_TP_CONTROL中DEEP_REMOTE_LPBK 置1,就可以设置成低速端内部自回环。

您好,

根据对recovered byte clock理解:

1.recovered byte clock = 高速侧线速率 / 高速侧serdes倍频数 = 10G / 20 = 0.5G;

2.CLKOUT引脚输出 = recovered byte clock / CLKOUT_div (Page.41) = 0.5G / 4 = 0.125G = 125M

今天在芯片LS_TX端未加信号基础上 ,分别enable PRBSEN和disable PRBSEN,测得如下现象:

1.enable PRBSEN时,CLKOUT输出频率为156.25M;

2.disable PRBSEN时,CLKOUT输出频率为125M;

不知以上现象如何解释,156.25M = 125M * 10 / 8

是否是哪些配置出现问题?

你好,

(1)首先你得确认一下你发送端的时钟是否正确,我简单推算了一下,当高速端data rate为12.5G时会出现clock out为156.25M。

(2)比较奇怪为什么PRBS disable后还有clock out.你能更详细介绍下你的连接和测试方法吗?

您好,

电路参考时钟为125M,使用默认配置(MPY = 20,FULL RATE),

1)根据Page.16公式,高速侧线速率 = Reference Clock Frequency * MPY / RateScale = 125M * 20 / 0.25 = 10G;

2) 在默认配置下,与LS_TX端相接的FPGA为综合通信部分,引脚无输出;

谢谢您的回复!

您好

补充下,我在测试时,是将一块芯片高速侧收发(SFP+)接在一起(一根光纤接在SFP+收发端);

您好:

补充下测试条件,我的高速侧接SFP+端口,测试时单芯片高速侧收发端用光纤接在一起了。

clockout 输出不对的问题解决了吗?建议你测一下你的板子的信号,可能板子有问题,条件允许的话换一块试试。我在Lab里面试了几次都没有问题。

您好,我也准备买TLK10022评估板,能留一下联系方式么,方便咨询。

谢谢对TI产品的支持,请找当地的FAE支持会更加方便有效。谢谢!