很郁闷 求高手帮助 ti dac5681z evm配置问题

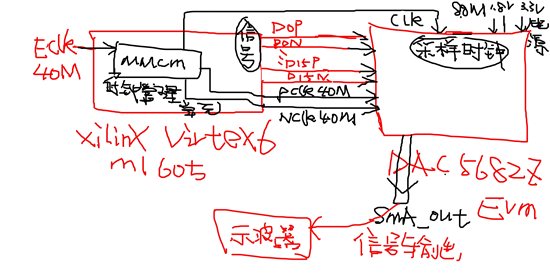

大家好,我最近用xilinx 的ML605 Virtex6的开发板,DAC转换器用的是TI 的5681z,我产生的信号中心频率大概是8M,带宽是3M左右的扫频信号,理论波形很好,用Matlab多次仿真了,但是DAC出来的信号质量很差,我想是不是我没有配置好,或者有其他问题导致的。

说明如下:

1 我用FPGA产生的信号,用 ti dac5681z evm评估板作为DA转换。

2 我用FPGA内部产生的时钟 dac随路时钟给的是40M,与FPGA产生的数据同源,我用40M的采样时钟供给 ti dac5681z evm 做为采样时钟,时钟质量相当好。

3 电源用的不是开关电源,都是几千块钱一台的特别好的电源,没有任何问题。

4 信号用一台安捷伦的仪器,生成比特文件后 da出来 信号质量很好。

5 TI公司在中国为什么连个电话技术支持都没有啊?! 哎 我的电话13621876343

6 附件中是我的配置 是不是哪地方没有配置好,还是其他原因?

请问,你说的信号质量很差,是哪方面的很差,有没有示波器截图?

您现在在哪个城市,TI在中国的技术支持网络,是非常广泛的。你可以直接联系就近的TI分公的找到我们的技术支持。

http://www.ti.com.cn/general/cn/docs/gencontent.tsp?contentId=28734

关于5681z的配置,请参照用户手册

http://www.ti.com.cn/cn/lit/ug/slau236a/slau236a.pdf

在你的描述中有两个疑问

2.“我用40M的采样时钟供给 ti dac5681z evm 做为采样时钟”,这个dacCLK转换时钟是什么芯片供给由fpga供给的么?FPGA只能用来做DATACLK随路时钟不能用来做转换时钟。转换时钟请使用专用时钟芯片如lmk04906

4. 如果你要测试DAC性能建议先用单音测试,不要用扫频信号。可以先用固定数据测试,然后用DDS即可

.接口时序是否正确?,测试方法手册43页

DIGITAL SELF TEST MODE

The DAC5681Z has a Digital Self Test (SLFTST) mode to designed to enable board level testing without

requiring specific input data test patterns. The SLFTST mode is enabled via the CONFIG1 SLFTST_ena bit and

results are only valid when CONFIG3 SLFTST_err_mask bit is cleared. An internal Linear Feedback Shift

Register (LFSR) is used to generate the input test patterns for the full test cycle while a checksum result is

computed on the digital signal chain outputs. The LVDS input data bus is ignored in SLFTST mode. After the test

cycle completes, if the checksum result does not match a hardwired comparison value, the STATUS4

SLFTST_err bit is set and will remain set until cleared by writing a ‘0’ to the SLFTST_err bit. A full self test cycle

requires no more than 400,000 CLKIN/C clock cycles to complete and will automatically repeat until the

SLFTEST_ena bit is cleared.

或者PATTERN测试

Pattern_err: A digital checkerboard pattern compare function is provided for board level confidence

testing and DLL limit checks. If the Pattern_err_mask bit via CONFIG3 is cleared, logic is

enabled to continuously monitor input FIFO data. Any received data pattern other than

0xAAAA or 0x5555 causes this bit to be set. To clear the error, flush out the previous

pattern error by inputting at least 8 samples of the 0xAAAA and/or 0x5555, then write a ‘0’

to this register bit.

5。你板子是在哪儿采购,TI在国内有800热线,全国各大城市都有分公司office. 你可以告知你所在城市,我叫当地代理给你电话

xue

把你DAC输出的波形给传上来大家看看吧

另外,你的采样时钟是由什么生成的?FPGA产生的时钟是不可以的

xu 感谢您的回复

我用fpga的ip核产生了4M的正弦信号进行测试,相位和幅值都不对,信号非常不稳定 我明天截图给你看

我在上海,调了5天5夜还没搞定 崩溃了 谢谢feng的回复

xilinx virtex 6 自带mmcm时钟管理单元 我用一个单端高精度温控晶振作为晶源产生的,晶源是40M,产生两路40M时钟,其中一路通过Fpga进行差分输出做为随路时钟,一路直接通过SMA接口输出做为采样时钟用频谱仪看时钟很稳定 谢谢你的回复liu

我用信号发生器当时钟用都不行。 我用的电压值为有效值1v 我用fpga 的mmcm时钟管理单元产生的信号 时钟质量很好 我的晶振一片就要800美金

larry:

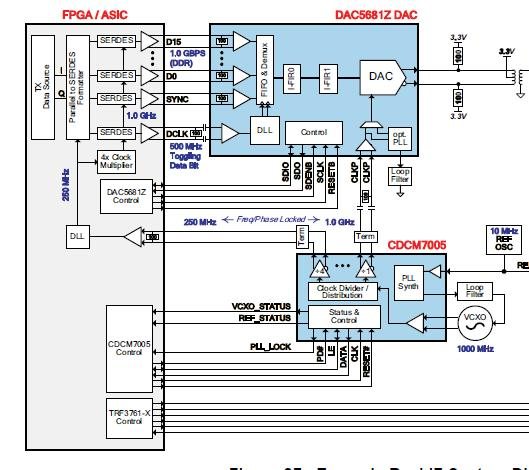

辛苦了,你看我们手册12页的figure3,4的效果很不错的.而且DAC5681Z, DAC5682Z在业界用量非常大,性能非常不错.所以主要检查下按照我们建议检查下基本的错误,

1.首先,FPGA只能用来提供data clk. 无论你的fpga有多么好,用得元件多么贵,由于其门电路的特征抖动, 用来做高速DAC的转换时钟是肯定不行的, 请用专用时钟芯片用Ultra Low Jitter Synthesizer and Jitter Cleaner来做高速DAC clk转换时钟.请看下面连接

http://www.ti.com/paramsearch/docs/parametricsearch.tsp?family=analog&familyId=351&uiTemplateId=NODE_STRY_PGE_T

2. 首先保证发dds单音否稳定干净. 然后确认接口时序是否正确,如我前文所说的测试方法,一定要保证接口正确,DAC才能正确的收到你所发的数据.

希望你能够明白系统中的关键因素, 能够有效地去debug.

信号接线图如图所示,我用fpga产生的16位的正弦信号,通过bufg原语差分输出,为什么信号质量输出后一个正弦波质量如此差哦。。。真是郁闷了 TI的东西靠谱不?