门电路与jitter

各位大神,

我想请问一个问题:时钟经过门电路会不会让jitter更差。

我的理解是这样的:门电路的tpd一般是会变化的,时钟经过门电路后,如果tpd在不停地变化,譬如从2ns~6ns。加入输入时钟是24.576MHz,那么T=40.7ns。考虑极限情况,前半周期tpd=2ns,后半周期tpd=6ns。

明显看出时钟频率变化。jitter明显增大。

可是我在TI的PLL芯片中也看到有门电路,如PLL1706,其中就有复用器。

请问我的理解是否正确?在音频电路中经常会是使用双时钟(22.5792MHz和24.576MHz),我现在使用的切换方案是使用复用器,请问这样可不可以,有没有更好的方案?谢谢!

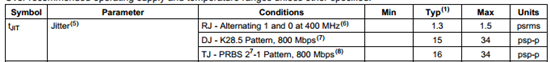

可以使用复用器的。复用器手册中一般会给出jitter值,这个值也就是综合了各种会影响jitter的参数得出的值。例如ds08mb200数据手册里给出

您好,

感谢您的回答,可是我在一些简单门电路数据手册中没有发现这项指标,如74HC08、74LVC2G157。ds08mv200的tpd、Ci和Co指标都要比74HC08和74LVC2G157好,请问这是不是ds08mv200 Jitter性能很好的原因呢?

如果门电路数据手册中没有这项指标,请问我该如何判断其jitter特性呢?谢谢!

如果是做极致级别的系统,需要重料CD机构(比如VRDS) + 高精度时钟同步整个系统. 这样的效果会是最接近完美的. 其次,就是不用重料CD机构,用随便什么东西,CD-ROM也行,然后还是Master Clock同步整个系统. 这样已能出非常好的效果. 再次,没有Master Clock同步系统的情况下,那么就要靠解码器的降jitter能力. 当然,这会是最主流的做法,因为高精度时钟代价不菲,大多数人使用不起,在此情况下,解码器端的降jitter能力就成为最普遍的需求.

一般来说是不会的,因为CMOS门电路的输出也是一个互补MOS推挽的输出,jitter一般都不会很差的。

如果没有这项指标,那就需要测量一下了,可以大概看一下眼图,先估计这个jitter有多大。你上面的理解tpd产生jitter是不对的,Tpd是传输延时,一般短时间内变化不大。Jitter主要是由电路的噪声产生判决门限变化而产生,这种表现为random jitter,这个值一般是很小的。

您的时钟部分对jitter要求有多高呢?

谢谢你的指点,我理解的确实有点问题,我后来在TI E2E上查到,LVC logic的jitter一般不会大于20ps,满足我的需求。

http://e2e.ti.com/support/logic/f/151/t/245461.aspx